המענה להתקררות חוק מור: שבבים תלת-מימדיים

30 יוני, 2015

עקב הקשיים הגוברים במיזעור שבבים, התעשייה מאמצת שיטות חדשות לשילוב פרוסות סיליקון שונות בתוך מארז-יחיד (3D-IC). המגמה נמצאת עדיין בתחילתה, אולם היא בעלת פוטנציאל רב מאוד

עקב הקשיים הגוברים במיזעור תהליכי ייצור השבבים, מאמצת התעשייה שיטות חדשות המבוססות על שילוב של פרוסות סיליקון שונות בתוך מארז-יחיד (3D-IC). המגמה נמצאת עדיין בתחילתה, אולם היא בעלת פוטנציאל רב מאוד

מאת: אדי סגל *

במהלך 50 השנים האחרונות טכנולוגיית המוליכים למחצה התקדמה באופן משמעותי, והיצרנים הצליחו לעמוד בקצב ההתקדמות שנקבע בחוק מור: צפיפות הטרנזיסטורים בשבב הוכפלה בכל 22 חודשים, תוך כדי שיפור הביצועים וצמצום צריכת ההספק. אוחם בשנים האחרונות התעשייה מתקשה לעמוד בקצב הזה. הקושי הטכנולוגי והעלות הגבוהה מאיטים את קצב המיזעור ברמת הסיליקון, ויצרני השבבים מאמצים בתגובה טכנולוגיות חדשות, דוגמת "השבב התלת-מימדי" (3D IC).

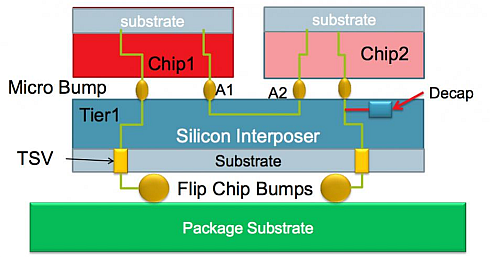

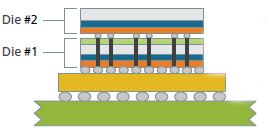

בטכנולוגיה זו משתמשים בשכבת סיליקון דקה (Silicon Interposer) שעליה מונחים מספר שבבים (Die) ומספקת את החיבורים החשמליים הדרושים בין השבבים כדי ליצור התקן אחד גדול. השבבים בהתקן כזה מסודרים בתצורה בה הם נמצאים זה לצד זה או בתצורה בה הם מונחים אחד על-גבי השני. טכנולוגיית השבב התלת-מימדי מאפשרת כיום לייצר רכיבים שצפיפות הטרנזיסטורים בהם גדולה יותר מהתחזית של חוק מור.

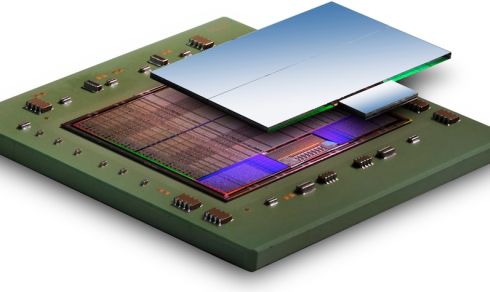

דוגמה טובה להתקנים מסוג זה הם רכיבי FPGA של חברת Xilinx ממשפחת Virtex-7. רכיבים אלו מיוצרים בטכנולוגיית 28nm 3D IC ומכילים 6.8 מיליארד טרנזיסטורים ו-2 מיליון תאים לוגיים. הצפיפות ברכיבי Virtex-7 גדולה בכמעט 40% מהרכיבים המקבילים מיוצרים בתהליך 28nm מונוליטי מסורתי.

ייצור ואינטגרציה של שבבים תלת-מימדיים

השבבים התלת-מימדיים מתחלקים לשני סוגים עיקריים: שבבים פאסיביים ושבבים אקטיביים. בשבבים הפאסיביים שכבת הסיליקון הדקה (Interposer) המחברת בין שניים או יותר שבבים אקטיביים לא מכילה טרנזיסטורים. בשבבים האקטיביים ( active-on-active 3D IC) כל מרכיב חוץ מהמצע של המארז, מכיל כמות מסויימת של טרנזיסטורים.

השבבים הפאסיביים מיוצרים במגוון טכנולוגיות שונות המתחלקות לשלוש קבוצות עיקריות. הקבוצה הראשונה מבוססת על הטכנולוגיה הוותיקה והזולה יחסית של (MCM (Multi Chip Modules. בטכנולוגיה הזו מחברים מספר שבבים ביחד בתוך מארז אחד גדול על-גבי מעגל מודפס קטן מאוד. הטכנולוגיה מבוססת על טכנולוגיות אריזה קיימות, שבהן מספר הכניסות והיציאות לרכיב הוא כמה מאות בודדות, ורוחב קווי החיבור קצת גדול מ-10μm.

הקבוצה השנייה מבוססת על טכנולוגיות Fan Out, טכנולוגיית EMIB של Intel וטכנולוגיות המבוססות על סוגים שונים של שכבות סיליקון. בקבוצה זו מספר הכניסות והיציאות הוא בסדר גודל של כמה אלפים ורוחב קווי החיבור הוא 10μm-1μm. הקבוצה השלישית מבוססת על טכנולוגיות כמו (Through-Silicon Via) TSV, uBump (micro-Bump) או Si fab.

טכנולוגיות אלה מכילות עשרות אלפי עד מאות אלפי כניסות ויציאות והחיבורים הפנימיים מבוססים על טכנולוגיית sub-micron או BEOL. שבבים המיוצרים בטכנולוגיות מהסוג הזה מצמצמים את צריכת ההספק באופן משמעותי, דבר שגורם לצמצום מספר החיבורים הדרושים לכניסות והיציאות. דוגמאות לטכנולוגיה מהסוג הזה היא שיטת Stacked-Silicon Interconnect של חברת Xilinx, או שיטת Chip on Wafer on Substrate) CoWos) של חברת TSMC.

קטגוריית השבבים התלת-מימדיים האקטיביים נמצאת עדיין רק בתחילת דרכה, ואפשר למצוא נכון להיום רק שבבי זיכרון כמו שבבי זיכרון Flash של חברת Samsung. השבבים המורכבים יותר עדיין נמצאים בתהליכי פיתוח מוקדמים.

שיקולים בייצור שבבים תלת-מימדיים

זמינות: נכון להיום, רק כמות קטנה של טכנולוגיות ייצור שבבים תלת-מימדיים נמצאת בשימוש, זה נכון גם לגבי הטכנולוגיות הפאסיביות וגם לגבי האקטיביות. מרבית הטכנולוגיות נמצאות עדיין בתהליכי פיתוח. אם יצרן שבבים מסויים מעוניין לאמץ את רעיון השבבים התלת-מימדיים, הוא חייב לבחור את הטכנולוגיה המתאימה ביותר ללוח הזמנים והתקציב שלו, מכיוון שחלק מהטכנולוגיות יהיו שימושיות רק בעתיד וחלק לא יהיו שימושיות בכלל.

תכנון המוצר: בעוד שכל השבבים התלת-מימדיים מספקים ביצועים טובים בהרבה בהשוואה לשבבים המסורתיים, המחיר שלהם הוא גבוה יותר. לכן חשוב לבדוק את העלות מול התועלת בשימוש בשבב תלת-מימדי במערכת המתוכננת.

ארכטיקטורה: השבב התלת-מימדי מבוסס בדרך-כלל על ארכטיקטורה שונה מהשבבים המונוליטיים המסורתיים. השוני בין הארכיטקטורות יכול ליצור בעיה במקרים בהם מחברים בין שבבים המבוססים על ארכטיקטורות שונות, ולכן חשוב לבחור את הארכיטקטורה הנכונה .

כלי-תכנון וסימולציה: תהליך תכנון השבב כולל סימולציות לשבבים שונים, וריפיקציה, מיקום וניתוב תיקיות של טכנולוגיות שונות. בשנים האחרונות הרבה חברות העוסקות בתחום התחילו לספק כלים המיועדים לתכנון וסימולציה של שבבים, אבל לא כל הכלים מכילים את כל הפונקציות הנדרשות. לכן קיימת חשיבות גדולה בבחירת הכלי המתאים הכולל את הסימולציות וכלי-התכנון המתאימים ביותר לדרישות הפיתוח.

תכנון תהליכי בדיקות (DFT) ובדיקת KGD: אחד מהפרמטרים החשובים ביותר בתהליך הבדיקה, במיוחד בשלבים הראשונים, הוא התפוקה (Yield), המבטא את שיעור המוצרים התקינים. לדוגמה אם שבב תלת-מימדי מכיל ארבי פרוסות סיליקון (dies), ובתהליך הבדיקה מגלים שרק אחת מהן פגומה, פירוש הדבר ששלוש האחרות יתפקדו בצורה בלתי תקינה. לכן חשוב מאוד לשלב את בדיקת (KNG (known-good-dies בתהליכי הבדיקות, על-מנת לגלות את ההפרוסה הפגומה לפני תהליך ההרכבה.

שרשרת אספקה: שרשרת האספקה בתהליך הייצור של שבבים תלת-מימדיים מורכבת מאוד וכוללת הרבה ספקים וקבלני משנה שונים. לדוגמה, מלבד ייצור והרכבת פרוסות הסיליקון, יש צורך גם לבצע אינטגרציה בין השבבים השונים, ולפעמים תהליכים אלה מתבצעים אצל קבלני משנה או ספקים שונים. ליצרני מצע המארז יש גם תפקיד חשוב מאוד בתהליך הייצור בגלל המעורבות שלהם בתכנון המכני, החשמלי ובתכנון התרמי. ההתחייבות הכלכלית בין הספקים השונים הופכת למסובכת יותר. לכן חשוב מאוד לנהל בצורה יעילה את כל שרשרת האספקה בתהליך הייצור.

* הכתבה מבוססת על המאמר בשם Next-generation 3D FPGAs שפורסם במגזין Chip Scale Review של חברת Xilinx.

פורסם בקטגוריות: חדשות , סמיקונדקטורס

פורסם בתגיות: featured