TSMC אישרה את קיידנס לייצור ב-7 ננומטר וב-5 ננומטר

23 מאי, 2018

כלי ה-signoff של קיידנס שאושרו כוללים טיפול בחיתוך מתכת (cut-metal) לכל אורך זרימת התכנון, תמיכת via-pillar, טכניקת clock mesh וניתוב אפיקים

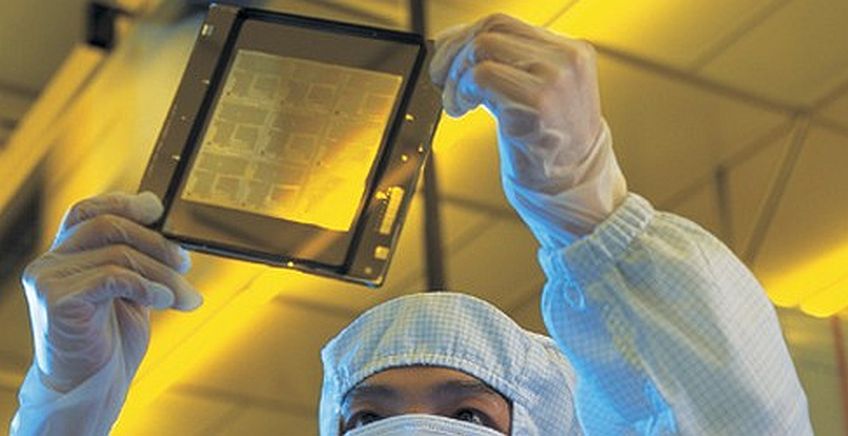

חברת קיידנס דיזיין סיסטמס (Cadence) הכריזה על שיתוף פעולה עם TSMC בפיתוח טכנולוגיות ייצור עבור שבבים המיוצרים מטרנזיסטורי FinFET בגודל צומת של 7 ננומטר ו-5 ננומטר, עבור מחשבים ניידים ומחשבים עתירי ביצועים (HPC). החברה מסרה שכלי הפיתוח שלה, דוגמת כלי signoff וכלים אנלוגיים, קיבלו את אישורי SPICE ו-Design Rule Manual של TSMC עבור תהליכי 5 ננומטר ו-7 ננומטר. כלי ה-signoff של קיידנס שאושרו כוללים טיפול בחיתוך מתכת (cut-metal) לכל אורך זרימת התכנון, תמיכת via-pillar, טכניקת clock mesh וניתוב אפיקים.

היכולות החדשות הכלולות ב-Virtuoso Advanced-Node Platform מאפשרות לשפר את תפוקת המימוש הפיסי של מעגלים אנלוגיים מסורתיים בהם אין מבנה מסודר וקשיח כמו במעגלים דיגיטליים. "בעזרת ה-PDKs וכללי התכנון החדשים, התחילו לקוחותינו לתכנן מערכות על-גבי שבב (SoCs) מורכבות על טכנולוגיות התהליך הכי מתקדמות שלנו", אמר סוק לי, מנהל בכיר בחטיבת שיווק תשתיות תכנון ב-TSMC. בנוסף, הודיעה קיידנס, שכל חבילת כלי תכנון המעגליים שלה (הדיגיטליים, ה-signoff והאנלוגיים), בשילוב עם פתרונות התכנון למארזי מעגלים משולבים, תומכים מעתה בטכנולוגית המערומים החדשה של TSMC.

בעזרת שיטת Wafer-on-Wafer (פרוסת סיליקון על גבי פרוסת סיליקון), קיידנס מספקת כלים המאפשרים ללקוחות TSMC לנהל את החיבוריות והאימות בפתרונות שילוב השבבים שלהם, כחלק מתהליך התכנון. הכלים של קיידנס מוטבו כדי לספק תזרים משולב ומלא עבור היישום של טכניקות שילוב שבבים ב-WoW בתוך שרשרת הכלים הקיימת. "לקיידנס היסטוריה עשירה של תמיכה בפתרונות TSMC, והתמיכה שלנו עבור טכנולוגיית WoW מבית TSMC מאפשרת למהנדסי התכנון לפרוס את טכניקות הזיווד החדשות ביותר ולצאת מהר יותר אל השוק", אמר טום בקלי, סגן נשיא בכיר ומנהל כללי בקבוצת ה-Custom & PCB בקיידנס.

פורסם בקטגוריות: חדשות , תוכנה ותכנון אלקטרוני