Xilinx הגדירה קטגוריה חדשה של "רכיבי מיחשוב מסתגל"

19 מרץ, 2018

זיילינקס הקציבה 1,500 מהנדסים ויותר ממיליארד דולר בפיתוח שבב ענק בן 50 מיליארד טרנזיסטורים המתאים את עצמו לצורכי המפתחים: החל מהפעלת בינה מלאכותית וחיפוש בבסיסי נתונים גדולים, וכלה בהפעלת מערכות הדור החמישי

חברת זיילינקס (Xilinx) ביצעה את ההכרזה החשובה ביותר שלה בשנים האחרונות, וחשפה קטגוריה חדשה בתחום הרכיבים המיתכנתים, בשם פלטפורמת מיחשוב והאצה מסתגלת (Adaptive Compute Acceleration Platform). מדובר בפרוייקט ענק שנמשך חמש שנים בהשקעה כוללת של כמעט 1.5 מיליארד דולר ובהשתתפות צוות של 1,500 מהנדסי חומרה ותוכנה.

נשיא ומנכ"ל זיילינקס, ויקטור פנג, אמר שמדובר ברעיון פורץ דרך בתעשייה. "זהו ההישג הטכנולוגי החשוב ביותר של זיילינקס מאז המצאת ה-FPGA. הארכיטקטורה הזו היא מרכיב באסטרטגיה כוללת של מעבר אל תחומים שמעבר ל-FPGA ומעבר לעולם של מהנדסי החומרה בלבד".

להערכת החברה, הפלטפורמה, אשר ניתנת לשינוי תצורה והגדרות תוך כדי עבודה, מספקת ביצועים לוואט שהם טובים יותר מאשר מפלטפורמות המבוססות על CPU או GPU. הפלטפורמה מיועדת להריץ יישומים חדשים בתחום הביג דטה והבינה המלאכותית, דוגמת המרת קידודים של קבצי וידאו, דחיסת מידע, חיפוש בבסיסי נתונים גדולים, יישום הסקות של מערכות לימוד עומק המבוססות על רשתות נוירוניות (AI inference), האצת רשתות יישומי ראיית מכונה ועוד.

הרכיב הראשוון במשפחת מוצרי ACAP קיבל את הכינוי אוורסט (Everest). הוא ייוצר בתהליך 7 ננומטר של חברת TSMC, כאשר הדוגמאות הראשונות שלו (tapeout) צפויות לצאת מקו הייצור מאוחר יותר השנה. האספקה המסחרית מתוכננת ל-2019.

פלטפורמת ACAP מותאמת למהנדסי חומרה ולמהנדסי תוכנה

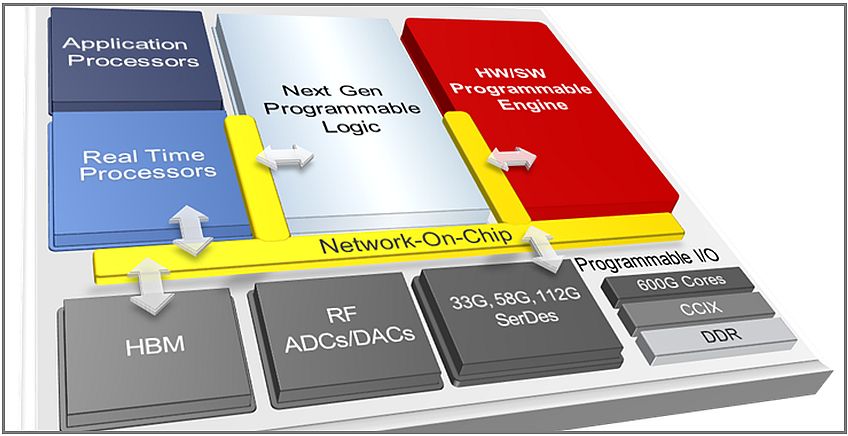

בבסיסה, פלטפורמת ACAP מבוססת על מארג FPGA מסוג חדש לחלוטין הנתמכת על-ידי תשתית רחבה של מעגלים. בהם: זיכרון מבוזר בתוך השבב, בלוקים הכוללים ליבות DSP, בלוקים של מעבדים מרובי-ליבות וליבות עיבוד מוגדרות תוכנה (software programmable compute engines) מאיצי עיבוד. כל המערך הז מקושר באמצעות רשת תקשורת פנימית בתוך השבב (NoC). בסך הכל, מדובר בשבב עצום הכולל כ-50 מיליארד טרנזיסטורים.

הרכיב כולל מעגלי-עזר נוספים. בהם: מעגלי בקרת אבטחה ומעגלי בקרת הספק, בקרי זיכרון מיתכנתים, בקרי וממשקי תקשורת מסוג Ethernet, SerDes, PCIe ו-CCIX. חלק מהרכיבים יופיעו גם עם ממירי ADC ו-DAC מיתכנתים ורחבי פס. בהתאם לאסטרטגיית הכניסה לשווקים חדשים ולמשתמשים מסוג חדש, ניתן יהיה לתכנת את הרכיבים ברמת ה-RTL בכלים הרגילים של תכנות רכיבי FPGA, אולם גם בשפות תכנות עיליות כמו C/C++, OpenCL ופייתון (Python), שבהן עובדים מהנדסי תוכנה.

בהודעה הרשמית שהופצה אתמול, העריכה זיילינקס שרכיב אוורסט יספק שיפור של פי 20 בביצועים של רשתות נויירוניות, בהשוואה לרכיב Virtex VU9P הנוכחי של החברה, המיוצר בגיאומטריה של 16 ננומטר. "מערכות תקשורת אלחוטית לדור החמישי המבוססות על אוורסט יספקו רוחב פס גדול פי ארבעה בהשוואה למימושים כיום המבוססים על 16 ננומטר".

פורסם בקטגוריות: חדשות , מחשבים ומערכות משובצות , סמיקונדקטורס