אינטל הכריזה על מעבדי CPU המופיעים במארז תלת-מימדי

11 יוני, 2020

שילבה ליבות עיבוד עיבוד מסוג Sunny Cove בתהליך של 10 ננומטר שפותחו בישראל, בתוך מארז תלת מימדי מסוג Foveros. הטכנולוגיה החדשה מותאמת גם לייצור מודולים המבוססים על רכיבי FPGA מיתכנתים

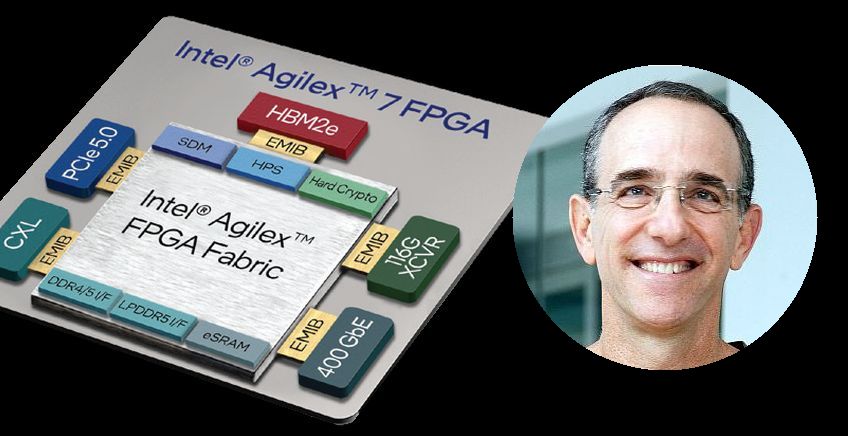

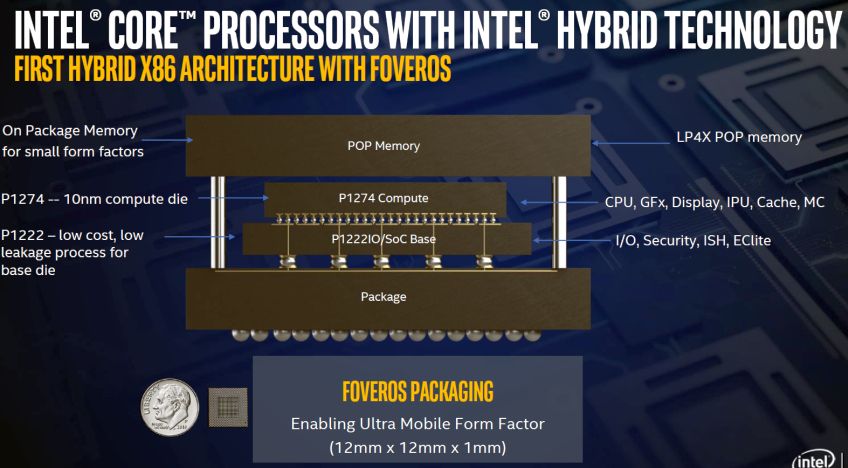

חברת אינטל (Intel) הכריזה אתמול על שבבים חדשים עבור מחשבים ניידים, אשר צורכים שטח קטן במיוחד מכיוון שהן מיוצרים בתוך מארז תלת-מימדי הכולל מספר שבבים נפרדים המסודרים בתצורת מגדל (Stack). אינטל העניקה להם את השם "מעבדים היברידיים" (Intel Hybrid). טכנולוגיית המארז נקראת Foveros. היא מאפשרת לקשר בין פיסות סיליקון המסודרות אחת על-גבי השנייה, ולצמצם ביותר מ-50% את השטח שהמעבד תופס על-גבי הלוח המודפס (PCB).

הרכיבים הראשונים בקטגוריית המעבדים ההיברידיים הם מעבדי Intel Core i5 ו-i3 המבוססים על ליבת 10nm Sunny Cove שפותחה באינטל ישראל. הם מגיעים במארז בשטח של 12 על 12 מ"מ, מריצים את מערכת ההפעלה חלונות ב-32 וב-64 סיביות (Windows 10) ומאפשרים לייצר מחשבים דקיקים וקלים מאוד. צמצום השטח התאפשר הודות להערמת שתי פיסות סיליקון (dies) לוגיות ושתי שכבות של DRAM, אחת על השנייה. הסידור הזה גם מבטל את הצורך להתקין זיכרון חיצוני לצד ה-CPU.

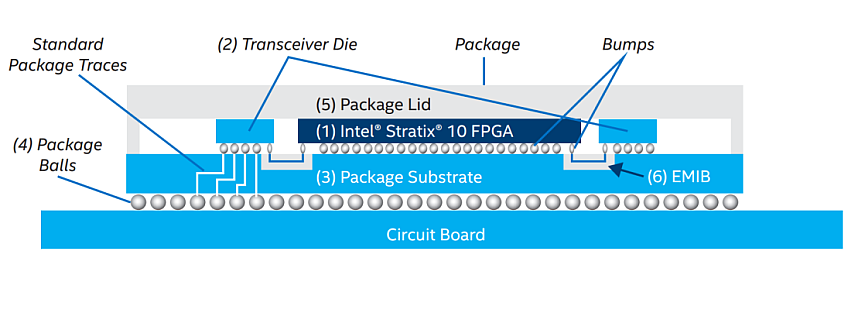

טכנולוגיית Foveros הוצגה לראשונה על-ידי אינטל בשנת 2019. היא מבוססת על שכבת בסיס לוגית ראשונית, שעליה ניתן להתקין שכבות לוגיות נוספות, למשל רכיבי CPU או רכיבי FPGA, ועליהן שכבות נוספות כמו מעגל אנלוגי או זכרונות. השכבות מקושרות אחת עם השניה באמצעות מגעים כדוריים זעירים המקשרים את המודולים החשמליים של פיסות הסיליקון.

הטכנולוגיה הזו נועדה לספק מענה לרכיבים מסוג חדש (Chiplets) שבהם מספר פרוסות סיליקון נפרדות מקושרות ישירות אחת אל השנייה ומספקות פונקציונליות גדולה. לגישה הזאת יש מספר יתרונות מובנים: ניתן להגיע לצפיפות מעשית גדולה מאוד גם בלא מעבר לתהליכי ייצור מתקדמים ויקרים שבהם רוחב הצומת של הטרנזיסטור קטן מ-10 ננומטר.

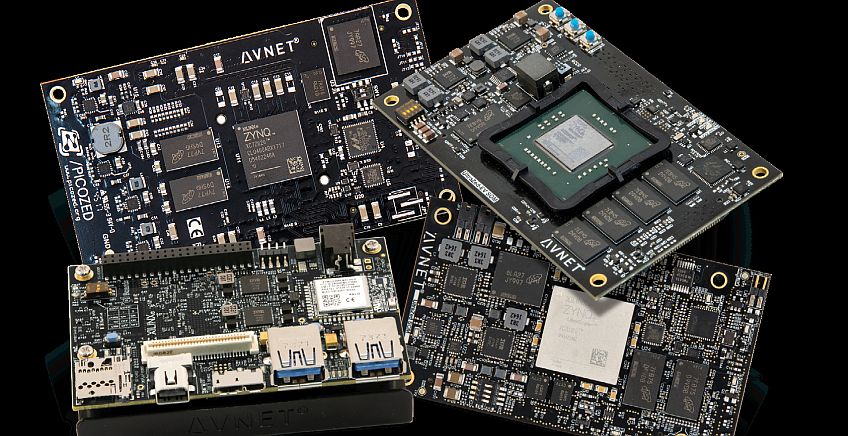

היא מאפשרת לייצר כל מודול בטכנולוגיית ייצור נפרדת, המותאמת אליו. כך למשל, במעגלים לוגיים יש יתרונות לשימוש בטרנזיסטורים קטנים, בעוד שבמעגלים אנלוגיים יש לעתים יתרונות דווקא לשימוש בטרנזיסטורים גדולים. כיום לא ניתן לייצר בפיסת סיליקון אחת מעגלים שיש בהם טרנזיסטורים בגדלים שונים. אינטל מקדמת את הטכנולוגיה גם בתחום הרכיבים המיתכנתים, ומציעה ללקוחות לייצר רכיבים מורכבים באמצעות שילוב ה-ASIC שלהם ביחד עם ה-FPGA של אינטל, במארז תלת-מימדי יחיד.

פורסם בקטגוריות: FPGA , חדשות , סמיקונדקטורס , רכיבים ופתרונות אלקטרוניים