FinFET נגד FD-SOI: מי ינצח במירוץ אל שבבי הדור הבא?

26 מאי, 2014

עמיעד קונלי מחברת Applied Materials חשף תופעה משונה במהלך הרצאתו בכנס ChipEx 2014. למרות היתרונות הברורים של טכנולוגיית FD-SOI, נראה שהיצרנים הגדולים החליטו לייצר את שבבי הדור הבא דווקא מטרנזיסטורי FinFET

אף שלטכנולוגיית FD-SOI יש יתרונות מובהקים, היצרנים הגדולים הולכים ל-FinFET

למרות ששחקנים מרכזיים בתעשיית ייצור השבבים, כמו אינטל ו-TSMC, כבר בחרו בטכנולוגיית FinFET כטכנולוגיית הייצור העתידית שלהם, הפיכתה לתקן תעשייתי אינה דבר בטוח. להערכת מנהל שיווק טכנולוגי בחברת Applied Materials Israel עמיעד קונלי, יש לטכנולוגיית Fully Depleted Silicon on Insulator המתחרה, הקרויה בקיצור FD-SOI, יתרונות משמעותיים שאי-אפשר להתעלם מהם.

בהרצאה בפני אנשי מקצוע שהעניק לאחרונה במהלך כנס ChipEx 2014, הוא אפילו אמר שהבחירה ב-FinFET אינה ברורה לגמרי, לאור היתרונות הגדולים של FD-SOI. מאחורי החיפוש אחר טכנולוגיות חדשות עומדת מציאות כלכלית-טכנולוגית: כאשר תהליך מיזעור הטרנזיסטורים בשבב הגיע לרמה של 20 ננומטר, התחלפה המגמה ששלטה בתעייה בשלושים השנים האחרונות.

עד אז, כל הקטנה של גודל הצומת הביאה להקטנה בעלות הטרנזיסטור (או השער) הבודד. ברגע שהתעשייה הגיעה ל-20 ננומטר, המגמה התהפכה והמחיר של כל טרנזיסטור החל לעלות. "במקביל, עלויות הפיתוח צומחות בצורה מעריכית וחברות קטנות פונות לפתרונות מבוססי FPGA, במקום לפתח רכיבי ASIC עצמיים".

אלא שחברות ענק המייצרות רכיבים למוצרים המוניים כמו מחשבים, טלפונים או מערכות מיחשוב לביש, לא יכולות להסתמך על רכיבי FPGA יקרים וגדולים. גבול ה-20 ננומטר התגלה גם כגבול טכנולוגי: "הזליגה בתוך הטרנזיסטור יוצרת בעיות הספק הולכות ומחמירות, עד למצב שבו טרנזיסטורים פלנאריים כבר לא מגיעים אף פעם למצבי OFF מלאים".

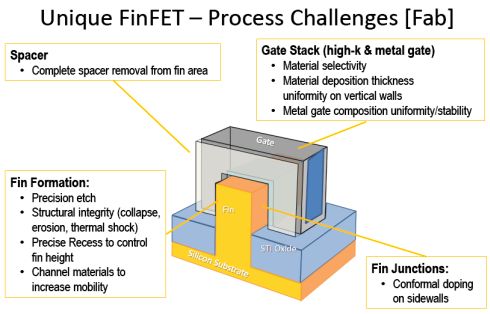

שתי הטכנולוגיות המתחרות על שבבי הדור הבא הן טכנולוגיית FinFET וטכנולוגיית FD-SOI. בטכנולוגיית FinFET השער האלקטרוני (Gate) מיוצר בצורה אנכית במקום אופקית, כדי להגדיל את שטח החתך של השער, לשפר את ביצועי הטרנזיסטור ולחסוך בהספק. ניתן לייצר את השערים בצורת סנפירים (Fins) באופן שבכל טרנזיסטור יהיו עד 3 סנפירים המגדילים משמעותית את שטח החתך של הצומת. חברת אינטל, למשל, בחרה בשיטה הזו (Tri-Gate).

טכנולוגיית FD-SOI שמרנית יותר: היא מבוססת על טכניקות היציור הפלנאריות המסורתיות, אולם שינויים במנה הצומת מאפשרים להפחית את מספר המטענים הדרוש כדי למתג את הטרנזיסטור, ובכך להפחית את הזליגה והקיבוליות הפראזיטיים ולהגביר את קצב המיתוג.

במהלך ההרצאה הישווה עמיעד בין היתרונות והחסרונות של שתי השיטות, גם ברמת הסיבוכיות של הייצור וגם ברמת הסיבוכיות של ציוד הבדיקה (מטרולוגיה) והגיע למסקנה ששתיהם נמצאות בתחרות צמודה מאוד, כאשר יש ל-FD-SOI מספר יתרונות מאוד בולטים. "טכנולוגיית FD-SOI חסכונית מאוד בהספק. הביצועים שלה דומים מאוד ל-FinFET, אולם השליטה בתהליך הייצור קלה יותר מאשר בטכנולוגיית FinFET".

פורסם בקטגוריות: חדשות , סמיקונדקטורס