Xilinx מייצרת את רכיבי UltraScale+ ב-16 ננומטר

1 מרץ, 2015

פלטפורמת הרכיבים המיתכנתים UltraScale+ של Xilinx כוללת גם שינויים במבנה הזיכרון, מירקם הקישוריות ועיבוד מרובה ליבות. היא מיועדת ליישומי LTE, רשתות סלולר מהדור החמישי, מערכות בטיחות ממונעות (ADAS) ועוד

פלטפורמת הרכיבים המיתכנתים UltraScale+ של Xilinx כוללת גם שינויים במבנה הזיכרון, מירקם הקישוריות ועיבוד מרובה ליבות. היא מיועדת ליישומי LTE, רשתות סלולר מהדור החמישי, מערכות בטיחות ממונעות (ADAS) ועוד

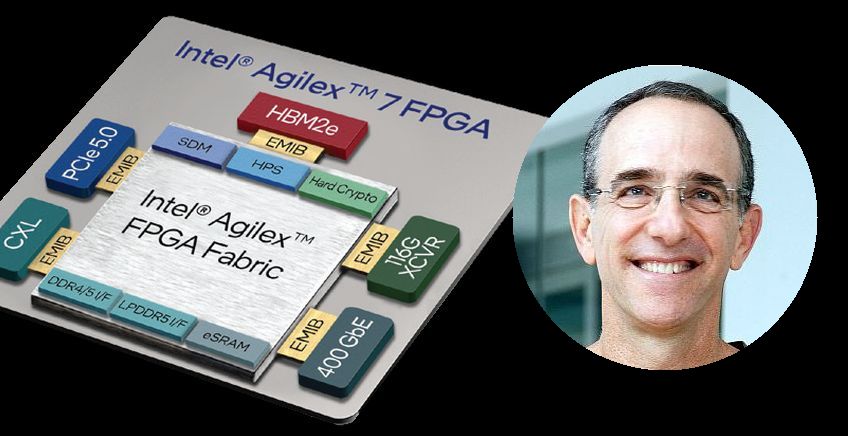

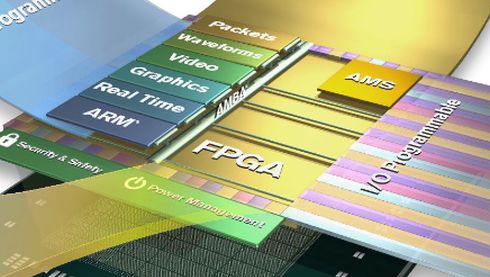

חברת Xilinx חשפה את פלטפורמת UltraScale+, שהיא פלטפורמת SoC חדשה של רכיבים מיתכנתים הכוללת את רכיבי ה-FPGA של החברה ממשפחות Kintex ו-Virtex. הרכיבים מיוצרים מטרנזיסטורי FinFET תלת מימדיים בתהליך הייצור של חברת TSMC. המשפחה החדשה כוללת מספר חידושים נוספים, בהם מבנה חדש של הזיכרון בשם UltraRAM, גישה חדשה בשם SmartConnect למירקם הקישוריות הפנימי ותשתית ריבוי ליבות בשם MPSoCs.

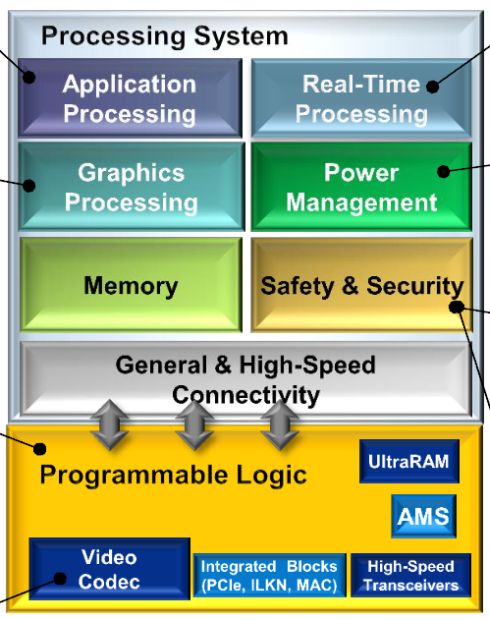

בליבת הארכיטקטורה נמצאים מעבדי ARM Cortex-A53 בעלי 64 סיביות וארבע ליבות, המסוגלים לתמוך בווירטואליזציית חומרה, עיבוד אסימטרי ותמיכה מלאה בטכנולוגיית האבטחה ARM TrustZone. להערכת החברה, הרכיבים החדשים מספקים שיפור של פי 2-5 בביצועים לוואר, בהשוואה לרכיבים המיתכנתים התוצרתה המיוצרים בטכנולוגיית 28 ננומטר.

מבנה חדש של הזיכרון

הזיכרון מהווה אחד מצווארי הבקבוק המשפיעים על תפקוד רכיבי FPGA ועל רכיבי SoC בכלל. מחד, לזיכרון פנימי ברכיב משקל כבד בצריכת ההספק שלו, ומאידך, הגישה לזיכרון חיצוני מעכבת מאוד את פעולת העיבוד הכוללת.

ארכיטקטורת UltraRAM נבנתה סביב פשרה המבוססת על שימוש בבלוקים גדולים של זיכרון SRAM פנימיים, בנפח של 288kBit לכל בלוק. נפח הזיכרון הכולל משתנה בהתאם לדגם הרכיב ויכול להגיע עד ל-432Mbits. מדובר בזיכרון פחות גמיש מאשר זיכרון חיצוני, אולם הוא מאפשר עיבוד מהיר הדורש חישובים אחידים על כמויות גדולות של נתונים, כמו למשל עיבוד וידאו. למעשה, מדובר במעין פתרון ביניים בין RAM לזיכרון חיצוני.

מירקם קישוריות על תנאי

מירקם SmartConnect מבצע פעולה מיוחדת: ארכיטקטורת UltraScale מתמודדת עם בעיות המירקם ברמת הסיליקון, ומבוססת על תכנון מחדש של החיבורים בין הבלוקים, פעולות השעון, המעגלים הלוגיים המקשרים בין המודולים בתוך הרכיב ועוד. טכנולוגית SmartConnect נמצאת ברמת הפשטה גבוהה יותר: למעשה זהו כלי הבוחר את הקישוריות המתאימה ביותר למערכת הנמצאת בתכנון.

המטרה היא להגיע לאופטימיזציה של השטח וההספק של כל מעגלים הקישוריות. במסגרת הזאת, הכלי יכול לזהות שחלק מהביצועים במירקם לוגי שניבחר אינם נחוצים, ואז הוא יכול לבטל את המרכיבים הלא נחוצים כדי לחסוך בשטח סיליקון ובהספק.

הקצה הגבוה של השוק

בשילוב עם משפחת Zynq, פלטפורמת UltraScale+ מציעה רכיבים עבור הקצה הגבוה ביותר של השוק, המוגדרים גם כבעלי יכולת עיבוד הטרוגנית: הם כוללים מעבד ARM מרובע ליבות בעל 64 סיביות (Cortex-A53) להרצת תוכנות ויישומים ברקע, מעבד ARM דו-ליבתי בעל 32 סיביות (Cortex-R5) למשימות זמן אמת קריטיות, מעבד גרפי Mali, ומעפנחי וידאו המוטמעים בשבב.

הרכיבים החדשים מיועדים לשימוש בכמה מהמוצרים הנתפסים כיום כמתפתחים ביותר בתעשייה: מוצרי תקשורת לרשתות LTE ולרשותת הסלולר הבאות מהדור החמישי (5G), מערכות עזר בטיחותיות לנהג (ADAS), קישוריות תעשייתית (Industrial IoT) UGUS/

חברת זיילנקס מתכננת להוציא לשוק 11 דגמים שונים במסגרת ההכרזה. לקוחות אסטרטגיים כבר קיבלו כלי-פיתוח. ברבעון השני השנה צפויים לצאת הרכיבים הראשונים מקו הייצור, והחברה נערכת לתחילת האספקה ההמונית ברבעון האחרון של 2015.

פורסם בקטגוריות: FPGA , MCU/MPU , חדשות , סמיקונדקטורס