RISC-V: שבבי הקוד הפתוח מגיעים אל השוק

23 דצמבר, 2016

שיתוף הפעולה בין חברת SiFive לבין חברת Microsemi פותח את שוק שבבי הקוד הפתוח: לאחרונה הן הכריזו על רכיב SoC המבוסס על מעבדי הקוד הפתוח RISC-V, והטמעת הארכיטקטורה ברכיבי FPGA

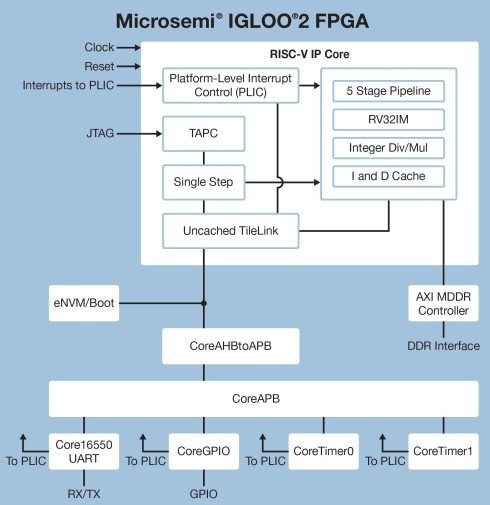

חברת Microsemi מקליפורניה, ארה"ב, מתחילה להסתמן כיצרנית השבבים הראשונה המגבשת אסטרטגיה מרכזית מסביב לרעיון הקוד-הפתוח ברמת הסיליקון. לאחרונה היא החלה לספק רכיבי FPGA מיתכנתים הכוללים את ליבת המעבד בקוד פתוח RISC-V. להערכת החברה היא הראשונה המספקת את המעבדים האלה על-גבי רכיבים מיתכנתים.

מדובר בליבת הארכיטקטורה ( RV32IM) וסביבת פיתוח (IDE) המאפשרת ליישם פונקציות שונות באמצעות הארכיטקטורה הזו. בשבוע שעבר היא הכריזה שליבת הארכיטקטורה תהיה זמינה על-גבי משפחות הרכיבים המיתכנתים: IGLOO-2, SmartFusion ו- RTG4. הם יופיעו ביחד עם סביבת הפיתוח SoftConsole אשר רצה על-גבי מערכת ההפעלה לינוקס, ועם מערך התמיכה Libero SoC Design Suite.

מהפיכת RISC-V

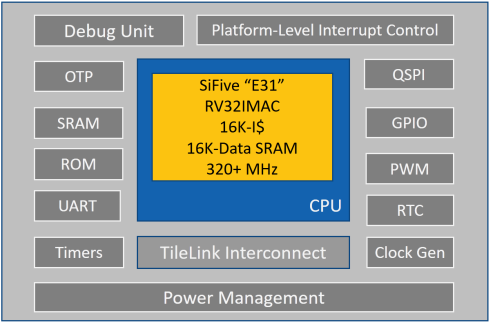

ליבת RV32IM RISC-V החדשה פותחה בשיתוף עם חברת SiFive, אשר הוקמה על-ידי צוות המפתחים המקורי של ארכיטקטורת RISC-V באוניברסיטת ברקלי, קליפורניה. כמעט כל השבבים בשוק כוללים כיום מעבד המבוסס על ארכיטקטורת פקודות (Instruction Set Architecture) בעלת זכויות יוצרים, שהשימוש בה דורש תשלום תמלוגים יקרים מאוד.

כדי להוזיל את העלויות של השימוש בארכיטקטורת המחשוב, פיתחו חוקרים באוניברסיטת ברקלי בקליפורניה גרסת קוד פתוח של ISA חדשה בשם RISC-V, שתוכל להריץ מעבדים חזקים מאוד, עד 128 סיביות.

הארכיטקטורה הזו מיועדת להריץ שרתים חזקים מאוד, מערכות משובצות זולות, ואפילו אבזרי IoT שהם חסכניים מאוד באנרגיה ובמשאבי עיבוד. כבר היום היא ניתנת בחינם באמצעות רישיון השימוש החופשי של האוניברסיטה (Berkeley Software Distribution).

ענקיות השבבים בודקות את הרעיון

אלא שהרעיון לא נשאר באקדמיה. בתחילת 2016 הוקם ארגון התמיכה התעשייתיRISC-V Foundation, שנועד להפיץ את השימוש בארכיטקטורת המחשוב החופשית. בינואר השנה דיווח האיגוד שהתמיכה התעשיית מתרחבת, וכיום הוא מקבל תקציב תמיכה מ-16 חברות גדולות בתעשייה. בהן: HP, גוגל, אורקל, מיקרוסמי, לאטיס ועוד.

פורסם בקטגוריות: חדשות , רכיבים ופתרונות אלקטרוניים

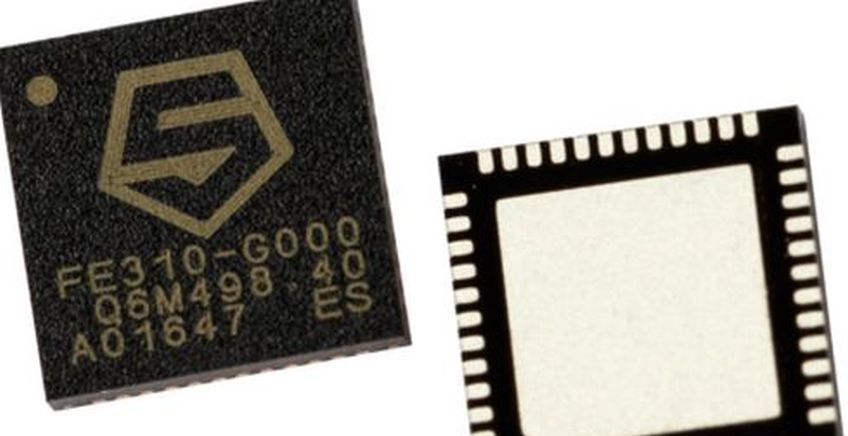

לפני שבועיים הכריזה SiFive על מה שניתן לכנות בשם שבב ה-SoC הפתוח הראשון בתעשיית השבבים. היא פיתחה מערכת על שבב בשם Freedom Everywhere 310 הכוללת ליבת עיבוד מבוססת RISC-V ומעגלי עזר סביבה דוגמת ממשקי תקשורת, זיכרונות מקומיים, מחלקי תדר ועוד. הרכיב נבחן באמצעות ייצור רכיב ממשי בחברת TSMC בגיאומטריה של 180 ננומטר.

לפני שבועיים הכריזה SiFive על מה שניתן לכנות בשם שבב ה-SoC הפתוח הראשון בתעשיית השבבים. היא פיתחה מערכת על שבב בשם Freedom Everywhere 310 הכוללת ליבת עיבוד מבוססת RISC-V ומעגלי עזר סביבה דוגמת ממשקי תקשורת, זיכרונות מקומיים, מחלקי תדר ועוד. הרכיב נבחן באמצעות ייצור רכיב ממשי בחברת TSMC בגיאומטריה של 180 ננומטר.