טקס ההתבגרות של מעבד הקוד הפתוח RISC-V

5 דצמבר, 2018

הוועידה הראשונה של ארגון RISC-V חשפה שיתוף פעולה בין ענקיות השבבים המעוניינות לקדם את רעיון המעבד החופשי בקוד פתוח. ווסטרן דיג'יטל פיתחה מעבד עצמי, ונערכת למכירת מיליארד מעבדים בשנה

השבוע מתקיים ארוע יוצא דופן בשוק השבבים: שלשום נפתחה בסנטה קלרה, קליפורניה, הוועידה השנתית הראשונה של ארגון RISC-V, אשר מקדם את המעבד החופשי שופתח באוניברסיטת ברקלי. רשימת החברות המשתתפות בכנס מגלה שמדובר כבר במהלך תעשייתי רחב היקף, ולא ביוזמה אקדמית משותפת: ווסטרן דיג'יטל, מיקרוסמי (הנמצאת בבעלות Microchip), קואלקום, NXP, לאטיס, RAMBUS, קוויק-לוג'יק, Andes הסינית ואפילו איגוד Linux Foundation.

האחרון הוא גוף חשוב מאוד אשר מייצג את המגמה: שבוע לפני הכנס דיווח איגוד הלינוקס על הסכם לשיתוף פעולה בין שני הארגונים, שמטרתו להעמיד לרשות משתמשי RISC-V את כל המשאבים של לינוקס ושל קהילת הקוד הפתוח שהיא מנהלת. בהתחשב בדמיון הרב בין תפישות העולם של שני הארגונים, ובדרך שבה הפכה לינוקס לתפועה מרכזית בתעשייה – שיתוף הפעולה מרמז על כניסה רחבת היקף של המעבד החופשי אל תעשיית השבבים.

קואליציית שבבי הקוד הפתוח

ארכיטקטורת RISC-V פותחה לפני כשמונה שנים באוניברסיטת ברקלי במתכונת של ממשק ISA שיכול להריץ מחשבים חזקים מאוד בביל אורך מילה של עד 128 סיביות. בשנת 2016 התעשייה החלה לאמץ את הרעיון והוקם ארגון התמיכה התעשייתי RISC-V Foundation, שנועד לקדם את השימוש בארכיטקטורת המחשוב החופשית.

כיום הארגון נתמך על-ידי כמה מהחברות החזקות בתעשייה, בהן: גוגל, HP, יבמ, אורקל, מיקרוסמי, לאטיס, אנבידיה, קואלקום, ווסטרן דיג'יטל, מארוול, מיקרון, NXP, סמסונג, וואווי, TSMC ועוד. גם התעשייה הישראלית מקדמת את מעבדי הקוד הפתוח. חברת מלאנוקס חברה בארגון במעמד של מייסד (founder), וחברת סיוה מהרצליה, שבעבר נכשלה ברכישת ארכיטקטורת MIPS, הצטרפה אליו במעמד של שותפה בכירה.

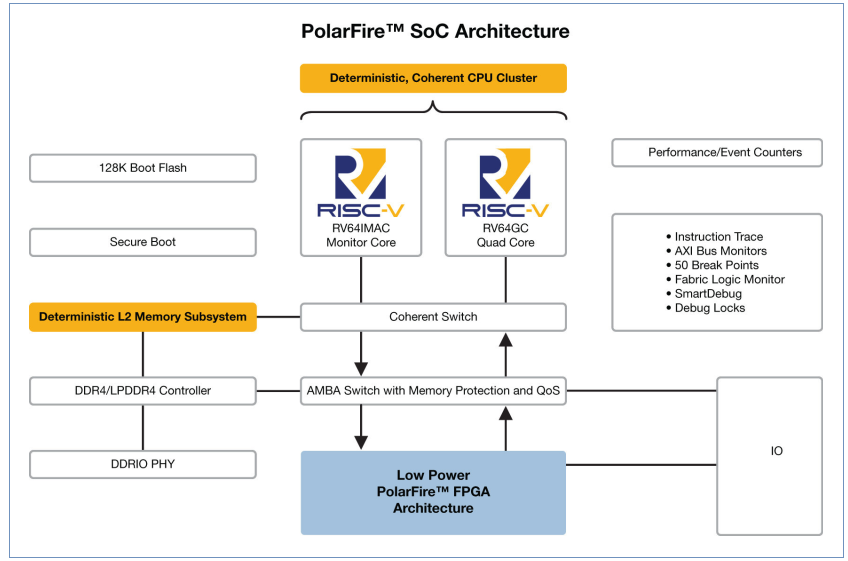

חברת מיקרוסמי חשפה בוועידה את ארכיטקטורת ה-SoC החדשה PolarFire, המיועדת לאשכולות מעבדים המנוהלים באמצעות לינוקס. הארכיטקטורה פותחה בשיתוף פעולה עם חברת SiFive, הנחשבת לחברה המובילה בפיתוח מסחרי של מעבדים מבוססי RISC-V, אשר הטמיעה בה את מעבד U54-MC מרובה הליבות שלה. היא כוללת מערך FPGA משובץ, זיכרון איתחול 128Kb flash ומערך איתחול מאובטח העומד בתקן צבאי. "זוהי פלטפורמה מיתכנתת שניתן להתאים אותה לכל צורך, היא מבוססת לינוקס ומיועדת למשימות זמן אמת", אמר מנכ"ל SiFive , נאביד שארוואמי.

השילוב של מערך FPGA משתלב במהלך תעשייתי נוסף: בחודש אוקטובר השנה הודיע ארגון RISC-V שהוא יפתח יישום חופשי לשימוש בכמעבד משובץ בתוך רכיבי FPGA. הדבר מאיים ישירות על חברת ARM אשר מוכרת תכנוני מעבדים (IP) שרבים מהם משובצים ברכיבי FPGA, ובתגובה היא הכריזה על שיתוף פעולה עם חברת Xilinx, שבמסגרתו היא תספק בחינם גרסאות מותאמות ל-FPGA של מעבדי Cortex-M, ללקוחות אשר ישבצו אותם בתוך הרכיבים של Xilinx.

היעד של ווסטרן דיג'יטל: מיליארד מעבדי RISC-V בשנה

הרעיון מתחיל להיכנס לשוק. חברת אנבידיה כבר התחילה להשתמש במעבדי RISC-V במספר מיקרו-בקרים, וחברת ווסטרן דיג'יטל (WD) הודיעה בתחילת השנה שבשנת 2019 או 2020 היא תוציא לשוק פתרונות איחסון המנוהלים באמצעות מעבדי RISC-V. אחת מהרצאות הפתיחה בפתיחת הפסגה שלשום היתה של הטכנולוג הראשי של WD, מרטין פינק, אשר דיווח על שלושה חידושי קוד פתוח של החברה, אשר נועדו לתמוך בצוות הפיתוח שלה של מעבדי RISC-V ואשר יועמדו גם לרשות קהילת הקוד הפתוח: החברה מתכננת להוציא לשוק קוד פתוח של מעבד RISC-V חדש, תקן OmniXtend לזיכרונות מטמון ברשתות איתרנט וערכת הפקודות הפתוחה SweRV Instruction Set Simulator, אשר יכולה לבצע סימולציות של RISC-V בתנאים שונים.

המאמצים האלה נעשים במסגרת יוזמה רחבה נועדה לשלב את המעבדים החדשים בתוך בקרי דיסקים. להערכת WD, היא תמכור דיסקים הכוללים מיליארדי מעבדי RISC-V בשנה. במסגרת זאת היא חשפה את מעבד RISC-V SweRV Core, הפועל באורך מילה של 32 סיביות ומאפשר ביצוע של מספר פקודות במקביל: הן נטענות ביחד למעבד ומובצעות מיידית. החברה דיווחה שהוא מגיע למהירות עבודה של 1.8Ghz כאשר הוא מיושם בטכנולוגיית CMOS בגיאומטריה של 28 ננומטר. ווסטרן דיג'יטל מתכננת להשתמש במעבדי SweRV במגוון תכנונים משובצים, בהם בקרי זכרונות פלאש ובקרים לכונני SSD. כל השפע הזה לא יישאר בידיה, ולדברי פינק, ווסטרן דיג'טל תעמיד אותו לרשותה של קהילת הקוד הפתוח.

פורסם בקטגוריות: חדשות , סמיקונדקטורס , קניין רוחני