במהלך כנס RISC-V Summit שהתקיים לפני כשבועיים בסין התבררה עובדה מפתיעה: סין הפכה למעצמת RISC-V גדולה ודינמית, בעלת השפעה עמוקה על ההתפתחות העולמית של ארכיטקטורת המחשוב הפתוחה. לכנס הגיעו 4,000 משתתפים מכל העולם, רובם מסין עצמה. במהלך הצגת הרכב הוועדות המקצועיות של ארגון RISC-V In International, התברר שנציגים סינים ממלאים בהן תפקידים בכירים ביותר, ומשמשים כיו"רים של ועדות מרכזיות כמו AI/ML SIG, Android SIG, Datacenter SIG, Platform Management Interface ועוד, ומשמשים סגני יו"ר בוועדות רבות נוספות.

הגילוי הזה חשף מהלך רחב היקף המתבצע בהובלה של ממשלת סין: הכוונת תעשיית הסמיקונדקטורס המקומית להיות המובילה העולמית בארכיטקטורת RISC-V הפתוחה, ולקדם אותה כתשתית מרכזית שתתחרה בארכיטקטורות הקנייניות מובילות היום בתעשייה, במיוחד x86 של אינטל ו-Arm של חברת ARM. המלחמה המסחרית הקרה המתנהלת בשני העשורים האחרונים בין המערב בראשות ארצות הברית לבין סין על השליטה בשק הסמיקונדקטורס העולמי, פגעה קשה ביעד שסין הציבה לעצמה לפני 15 שנים: להיות מעצמת שבבים עצמאית עד לשנת 2025.

אלא שכעת מתברר שסין מצאה מסלול עוקף סנקציות שיאפשר לה לממש את החזון הלאומי: התמחות בפיתוח וייצור שבבים המבוססים על ארכיטקטורת RISC-V הפתוחה. בחודש מרץ 2025 דיווחה סוכנות רויטרס שממשלת סין מתכננת לפרסם עוד השנה הנחייה גורפת שנועדה לעודד יצרניות שבבים וספקיות שירותי תכנון ותוכנה, לאמץ את ארכיטקטורת RISC-V. ההנחיות ותקציבי העידוד הנלווים, גובשו בקבוצת עבודה שכללה 8 סוכנויות ממשלתיות, בהן: מנהלת הגנת הסייבר, משרד התעשייה, משרד המדע והטכנולוגיה ומנהלת הקניין הרוחני הלאומית של סין.

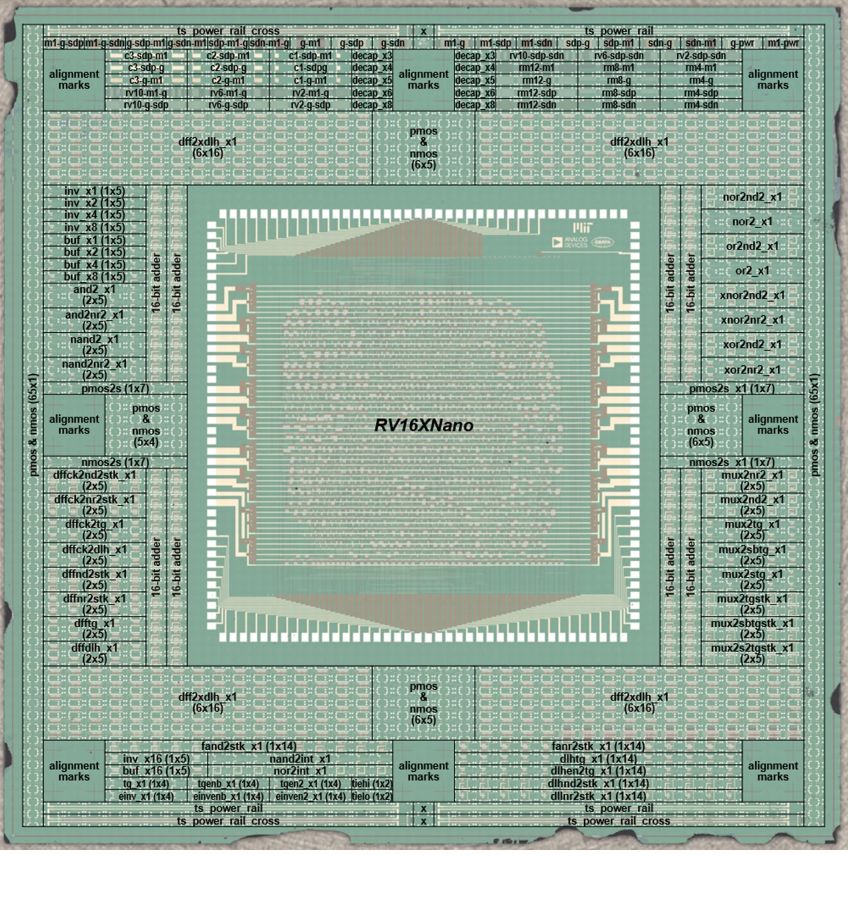

בשורת מעבדי הקוד הפתוח

ארכיטקטורת RISC-V פותחה לפני כ-15 שנים על-ידי מספר חוקרים מאוניברסיטת ברקלי, ארה"ב, אשר פירסמו גרסת קוד פתוחשל ממשק ISA אשר שיכול להריץ מחשבים חזקים מאוד בעלי אורך מילה של עד 128 סיביות. המטרה הייתה לספק אלטרנטיבה זולה לעלויות הגבוהות של השימוש בארכיטקטורות הקנייניות המסחריות המצויות בשוק. בשנים האחרונות נוצרה תעשייה גדלה ומתפתחת סביב RISC-V, וכעת הנתונים מראים שהיא עושה את דרכה אל ליבת השוק.

The SHD Group: Market Unit Shipments for All RISC-V SoCs by Application 2021–2030

להערכת חברת המחקר The SHD Group, ההכנסות ממכירת שבבי RISC-V בשנת 2023 הסתכמו בכ-123 מיליון דולר, אולם הן יצמחו בקצב שני של 39% עד 2030. באותה שנה יימכרו בשוק 16.5 מיליארד רכיבי SoC מבוססי RISC-V, בהיקף של כ-92 מיליארד דולר. מהמחקר עולים נתונים מעניינים נוספים: השוק הגדול ביותר של הארכיטקטורה הזו בשנת 2030 יהיה של רכיבים להאצת AI, שוק היעד הגדול ביותר יהיה שוק מוצרי הצריכה, והמגזר המרכזי יהיה תעשיית הרכב, שהוא מגזר צמיחה מרכזי של סין.

The SHD Group: Total RISC-V SoC Regional Revenues 2021-2030

האם סין תטיל מגבלות על ארה"ב?

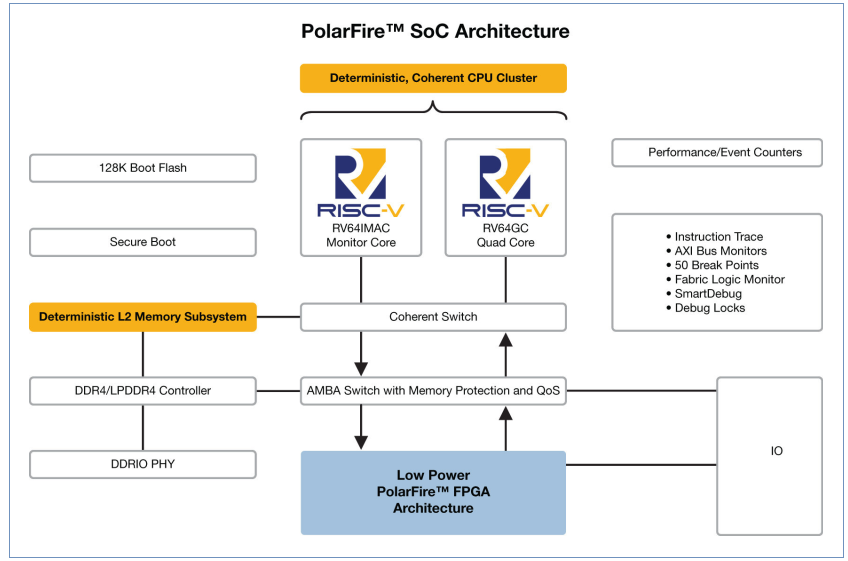

כללית, עד 2030 סין צפויה להיות הספקית הגדולה בעולם של פתרונות מבוססי RISC-V. אלא שהמחקר הזה פורסם בינואר 2024, והוא לא לוקח בחשבון את השפעת המדיניות החדשה של סין ואת עוצמת התגובה שלה להגבלות המחמירות של ממשל טראמפ. משמעות המדיניות החדשה היא לא שסין תוביל את שוק רכיבי ה-SoC מבוססי RISC-V, אלא שהיא תהפוך את הארכיטקטורה הזו לאבן יסוד של תעשיית שבבים עלית' שתאפשר לה לייצר מעבדי NPU, CPU ו-GPU מבוססי RISC-V וסביבת פיתוח תוכנה ייעודית עבורם (בעבר היא ניסתה לבצע מהלך דומה על בסיס ארכיטקטורת PowerPC הישנה, אולם נכשלה).

הדבר מייצר מציאות מעניינת: המירוץ המערבי אחר טכנולוגיות מתקדמות התבטא בהשקעות גדולות מאוד בטכנולוגיות ייצור חדשות ברוחב צומת של פחות מ-10 ננומטר, אולם לא ניתן לייצר ציוד אלקטרוני ללא רכיבים נלווים המיוצרים בתהליכים ישנים יותר של 28, 65 ואפילו 130 ננומטר. ברמת הייצור הזו, סין היא אחת מהיצרניות הגדולות בעולם. פירוש הדבר שאם אסטרטגיית ה-RISC-V תביא לה את הטכנולוגיות המתקדמות, היא תהיה זו שתוכל להטיל מגבלות על המערב – באמצעות הגבלות על מכירת רכיבים המיוצרים בתהליכי ייצור ישנים.