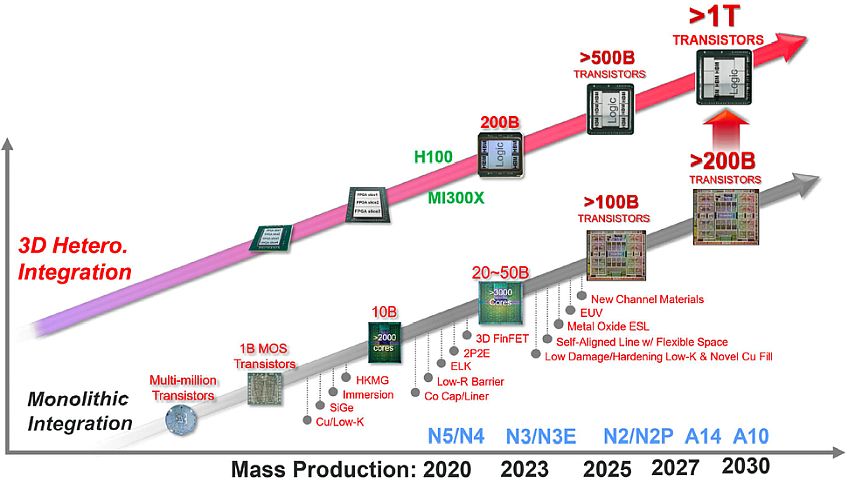

חברת TSMC מתכננת להגיע ליכולת ייצור של שבבים בעלי 200 מיליארד טרנזיסטורים עד לשנת 2030, ולצורך זה החלה בפיתוח תהליכי ייצור חדשים של 2 ננומטר, 1.4 ננומטר ו-1 ננומטר. האתר tom'sHARDWARE מדווח שהמידע הזה נמסר לתעשייה על-ידי החברה עצמה, בהרצאתו של מנהל טכנולוגיות המידע של TSMC, כריס לין, במהלך כנס IEDM שהתקיים לפני כשבועיים בסן פרנסיסקו. במקביל, TSMC מפתחת לדבריו גם טכנולוגיות מארזים חדשות (CoWoS, InFO, SoIC) במטרה לאפשר לה לייצר שבבים מרובי-אריחים (Chiplets) הכוללים יותר מטריליון טרנזיסטורים במארז יחיד.

מהשקף של החברה שהוצג בכנס, מתברר ש-TSMC כבר העניקה את הכינויים המסחריים של התהליכים החדשים. בשנת 2025 היא תציג את טכנולוגיית N2/N2P בגאומטריה של 2 ננומטר שתאפשר לה לייצר שבבים הכוללים כ-100 מיליארד טרנזיסטורים בפיסת סיליקון יחידה. במתכונת מרובת-אריחים, שהחברה מכנה בשם 3D Hetero Integration, ניתן יהיה לייצר רכיבים הכוללים כחצי מיליארד טרנזיסטורים. לאחר מכן היא תעבור לטכנולוגיית ביניים של 1.4 ננומטר שקיבלה את הכינוי A14.

היעד הוא להגיע לשנת 2030 עם טכנולוגיית 1 ננומטר בשם A10, אשר תאפשר לה לייצר רכיבי 3D הכוללים יותר ממיליארד טרנזיסטורים. להערכת החברה, זוהי המגמה הבולטת ביותר שתקבע את עתיד תעשיית השבבים: בגלל הקושי העצום הכרוך בייצור שבבים מרובי טרנזיסטורים על-גבי פיסת סיליקון יחידה, התעשייה תאמץ בהדרגה את גישת הרכיבים מרובי-אריחים, אשר תהיה הדומיננטית בשוק. יחד עם זאת, יחידות העיבוד עצמן (דוגמת CPUs) ימשיכו להתבסס על פרוסות סיליקון בודדות, ולהערכת החברה הן יזדקקו לפחות לכ-200 מיליון טרנזיסטורים כדי לתמוך בצורכי התעשייה בשנים הבאות.