פריסקייל חושפת את ארכיטקטורת Layerscape למעבדי QorIQ

11 יולי, 2012

היא מיועדת להתמודד עם דרישות הגמישות הגדלות של יצרניות OEM בתחום תשתיות הרשת, אשר צריכות להתאים עצמן לריבוי התקנים מקושרים, בסיס נתונים מסיביים, צורכי אבטחה מחמירים ומאפייני תעבורה קשים לחיזוי

חברת פריסקייל (Freescale) חשפה את ארכיטקטורת Layerscape החדשה, שעליה יתבססו מעבדי QorIQ מרובי-הליבות מהדור השלישי.

מדובר בארכיטקטורת חדשה המיועדת להאיץ את הפיתוח והביצועים של אבזרי רשת. היא מבוססת על הצורך של המעבדים להתאים את פעולתם לצורכי התוכנה כדי להעניק יותר גמישות ליצרניות OEM בתחום תשתיות הרשת, אשר צריכות להתאים עצמן לריבוי התקנים מקושרים, בסיס נתונים מסיביים, צורכי אבטחה מחמירים ומאפייני תעבורה קשים לחיזוי.

מדובר בארכיטקטורת חדשה המיועדת להאיץ את הפיתוח והביצועים של אבזרי רשת. היא מבוססת על הצורך של המעבדים להתאים את פעולתם לצורכי התוכנה כדי להעניק יותר גמישות ליצרניות OEM בתחום תשתיות הרשת, אשר צריכות להתאים עצמן לריבוי התקנים מקושרים, בסיס נתונים מסיביים, צורכי אבטחה מחמירים ומאפייני תעבורה קשים לחיזוי.

ארכיטקטורה תלת-שכבתית

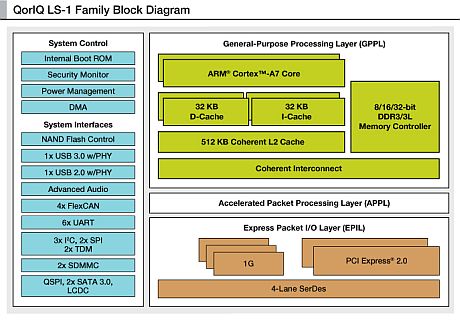

ארכיטקטורת Layerscape המודולרית מורכבת משלוש שכבות עצמאיות: שכבת עיבוד כללית (GPPL) המספקת ביצועי חישוב למטרת כלליות. שכבה זו ממוטבת עבור שירותי ענן וירטואליים ועבור יישומים במישור הבקרה. שכבת העיבוד להאצת חבילות מידע (APPL) מבצעת עיבוד חבילות מידע באופן אוטונומי ומאפשרת לתכנת יכולות מיוחדות במודל הרצה-להשלמה סינכרוני וסדרתי, המפשט את המיקרו-ארכיטקטורה של החומרה, ומעניק מודל תכנות משובץ מבוסס שפת C. שכבת הקלט/פלט לחבילות מידע מהירות (EPIL) מסייעת להשגת ביצועים אמיתיים ומוגדרים ברמת החיווט בין ממשקי רשת (עד ל-100 ג'יגה), תוך תמיכה ביכולות עבור L2 ומעלה.

הארכיטקטורה מווסתת את האצת חבילות המידע ומפשטת את האינטראקציה בין שכבות התקשורת. "הפכנו את המודעות לתוכנה לחלק אינטגרלי מהארכיטקטורה שלנו, אמר נשיא ומנכ"ל פריסקייל ישראל, דודי גלנטי. "אנחנו מאיצים את ה-IQ של הרשת עם חידושים הכוללים תאימות שאינה תלויה בליבות, עם עיבוד חבילות מידע עצמאי ויעיל יותר ועם יכולת ויזואליזציה בזמן אמת". מנכ"ל משותף פריסקייל ישראל, שמואל ברקן, אמר שהארכיטקטורה מיועדת לספק ללקוחות גמישות רבה בפיתוח המוצרים.

מוצרים ראשונים מבוססי Layerscape

מוצרים ראשונים מבוססי Layerscape

שתי משפחות מוצרי ה-QorIQ הראשונות המבוססות על ארכיטקטורת ה-Layerscape הן ה-LS-1 וה-LS-2. בין הדגשים של המשפחות הללו ניתן למצוא ליבות מעבד מבוססות ARM Cortex, תמיכה בווירטואליזציה, אבטחה מתקדמת, מערך מתקדם של חיבורים, תמיכה ב-ISA ותאימות מבחינת תוכנה ופינים להמרת יישומים חלקה בין שתי המשפחות.

משפחת ה-LS-1 כוללת שתי ליבות ARM Cortex-A7 שפועלות במהירות מרבית של 1.2GHz ובצריכת הספק נמוכה מ-3W. משפחת ה-LS-2 כוללת שתי ליבות ARM Cortex-A15 במהירות של עד 1.5GHz ובצריכת הספק של עד 5W. יישומי המטרה של משפחות LS-1 ו-LS-2 כוללים בקרת שערים בבתי מגורים, נקודות גישה ארגוניות, מערכות אנרגיה חכמה, תקשורת תעשייתית, כרטיסי קו ורובוטיקה.

פורסם בקטגוריות: DSP , MCU/MPU , חדשות , סמיקונדקטורס