Synopsys פיתחה פלטפורמה לתכנון רכיבי SoC

30 דצמבר, 2014

פלטפורמת Verification Continuum של Synopsys כוללת ממשק אחיד לכל שלבי האימות, שימוש בכלים קיימים, ופתרונות חומרה מבוססי FPGA שפותחו בעקבות שיתוף פעולה אסטרטגי עם Xilinx

פלטפורמת Verification Continuum של Synopsys כוללת ממשק אחיד לכל שלבי האימות, שימוש בכלים קיימים, ופתרונות חומרה מבוססי FPGA שפותחו בעקבות שיתוף פעולה אסטרטגי עם Xilinx

חברת Synopsys פיתחה פלטפורמת אימות חדשה בשם Verification Continuum, אשר מיועדת לקצר את זמני הפיתוח של רכיבים מורכבים מאוד (SoC). מנהל שיווק קבוצת האימות (Verification) בחברת סינופסיס, תום בורגסטרום, סיפר בראיון ל-Techtime שהפלטפורמה החדשה פותחה בשיתוף פעולה עם לקוחות אסטרטגיים של החברה ועל בסיס כלים קיימים של סינופסיס. "הצגנו אותה בהדרגה במהלך השנה, ומתחילת שנת 2015 היא תהיה בשלב הייצור המלא (Production), כלומר ניתן יהיה לרכוש אותה במלואה".

מדוע יש צורך לפתח פלטפורמה חדשה?

בורגסטרום: "הריבוי של רכיבי SoC גדולים יצר בעייה בתעשייה. שלבי התיכנון והאימות של שבבים דורשים שימוש בכלים שונים, כמו Simulation, Emulation, Prototyping ועוד. המעבר ביניהם נמשך זמן רב ולא תמיד יש תאימות מלאה בין הכלים. התוצאה היא שהאימות נמשך זמן רב מאוד מכיוון שתהליך התכנון כולל מעבר בין השלבים השונים, זיהוי בעיות (Debugging), תיקן הבעיות, וביצוע חוזר של כל התהליך מההתחלה.

"לפני מספר שנים במהלך שיחות עם לקוחות התחלנו להעלות רעיון חדש: להעביר פעולות אימות לתחילת תהליך התכנון כדי לאתר יותר באגים גבר בשלבים הראשונים. מכיוון ששלבי התכנון מתוארים בסכימות כמעבר משמאל לימין, כינינו את הרעיון החדש בשם Shift Left. להערכתו, היכולת לדבג את התכנון בשלבים המוקדמים יכול לקצר את זמני האימות של שבבים חדשים במספר חודשים.

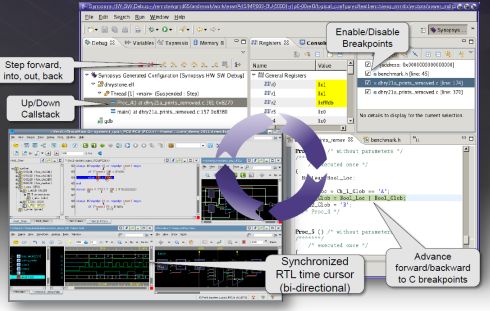

כדי לממש את הרעיון שילבה סינופסיס מספר כלים קיימים בתוך מסגרת אחת: תוכנת Virtualizer, תוכנת Verification Compile, פלטפורמת הסימולציה VCS, שרת האמולציה ZeBu וחומרת הפרוטוטייפינג HAPS. אחד ממרכיבי היסוד בפלטפורמת Verification Continuum הוא השימוש בממשק Verdi, אשר משמש ממשק אימות אחיד לכל שלבי הבדיקות, החל משלב ה-Virtual Prototyping ועד לשלב הסופי של FPGA-based Prototyping.

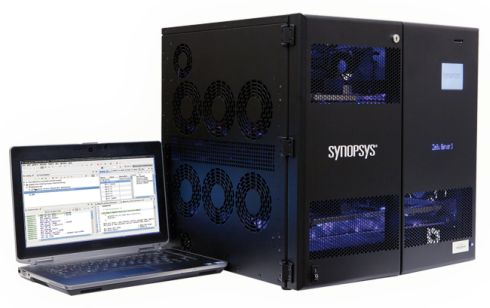

אחד ממרכיבי החומרה המעניינים של פלטפורמת Verification Continuum, הוא השרת ZeBu Server-3. מדובר בחומרה להרצת הסימולציה אשר מכילה מיליוני שערים לוגיים המיושמים באמצעות רכיבי FPGA של חברת Xilinx. היא מבוססת של שיתוף פעולה אסטרטגי שהחל השנה בין חברת Synopsys לבין חברת Xilinx. במסגרת הזאת, גם כרטיסי הפרוטוטיפינג מבוסבי FPGA, מבוססים על רכיבים של זיילינקס.

לדברי בורגסטרום, מטרת שיתוף הפעולה עם זיילינקס היא להפוך את האמולציה מבוססת FPGA לתהליך המוביל בתעשיית השבבים. "אנחנו סבורים שטכנולוגיית האמולציה תעבור שינוי ניכר בשנים הקרובות, ותתבסס בעתיד על רכיבי FPGA מסחריים".

פורסם בקטגוריות: חדשות , סרטי וידאו , תוכנה ותכנון אלקטרוני