קיידנס הכריזה על תאימות לתהליכי 5/6/7 ננומטר של TSMC

11 יוני, 2020

חברת קיידנס (Cadence) הודיעה על השלמת השינויים בחבילת כלי התכנון שלה למעגלים אנלוגיים ודיגיטליים, שנועדו להתאימם לתהליכי הייצור החדשים של חברת TSMC, בגיאומטריה של 5 ננומטר ושל 6 ננומטר (N6 ו-N5/N5P). השיוניים קיבלו הסמכהוכעת שתי החברות עובדות עם כ-25 לקוחות על תהליך N5/NP5 ועם כ-80 לקוחות על תהליכי N7/N6.

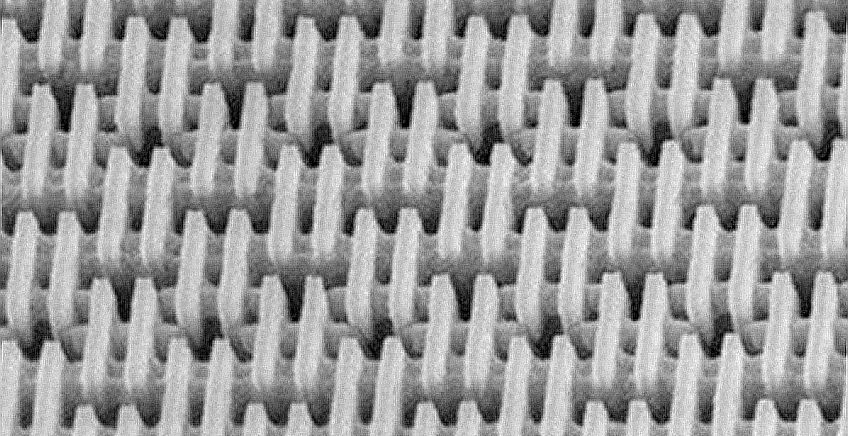

השיפורים בחבילת הכלים העדכנית כוללים תמיכה משופרת לשכבת EUV, בודק אינטגרציית שבבים חדש עבור כללי תכנון תכנית-רצפה ותוספות באמצעות via pillar, autoNDR ותמיכת SHDMIMCAP. בנוסף, בוצעו שיפורים במתודולוגיות התכנון וביכולות של פלטפורמת Virtuoso Advanced-Node, שהותאמה לתהליכים החדשים של TSMC.

ברמת ה-IP, החברה הכריזה על הזמינות של 56G long-reach SerDes IP עבור ייצור בתהליכי N7 ו-N6 של TSMC. מדובר בהרחבת חבילת פתרונות PAM4 SerDes. הערוץ החדש מיועד לשימוש במערכות 5G, מעבדי שרתים, ותכנוני SoC (מערכת על שבב) הכוללים למידת מכונה.

הוא כולל יכולת שחזור נתונים באמצעות ארכיטקטורה מבוססת DSP הניתנת לתכנות, כדי לקבל הספק מיטבי עבור מרחק נתון. להערכת החברה הוא מאפשר ללקוחות להשתמש ב-PCBs זולים יותר ולהשיג גמישות מרובה יותר בתכנון המערכת.

פורסם בקטגוריות: חדשות , רכיבים ופתרונות אלקטרוניים , תוכנה ותכנון אלקטרוני