סינופסיס משיקה גרסה חדשה של IC Compiler II

4 אפריל, 2017

הגירסה החדשה של IC Compiler II משפרת את איכות התוצאות (Quality of Results) ומספקת שיפור של 5% בשטח, 5% באיכות תוצאות התזמון (timing QoR) והפחתה של עד ל-20% בצריכת ההספק

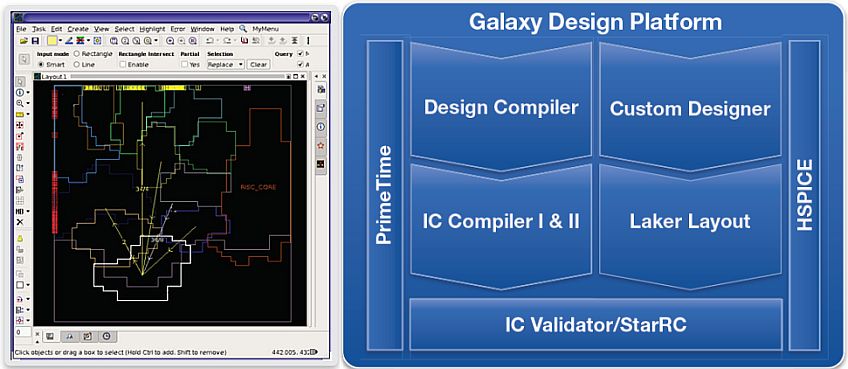

חברת סינופסיס (Synopsys) משיקה את IC Compiler II, מוצר הדגל של החברה עבור פתרונות ה-place-and-route. החברה מסרה שעבד היום היא שימש אצל יותר מ-100 לקוחות לעבוד על כ-250 תכנונים לייצור, המקיפים כמה אלפי מודולים פיסיים (physical partitions). הגרסה החדשה זמינה באופן מיידי וכוללת שיפורים המשפיעים ישירות על איכות התוצאות (QoR – Quality of Results) ומהירות השגת התוצאות (TTR – Time to Results) ביישומים מורכבים בעלי תלות קריטית בביצועים אלו. הגרסה החדשה כוללת יכולות דוגמת automatic-placement-clustering, advanced-logic-structuring, אופטימיזציה מקבילית של שעון ונתונים ((clock and data – CCD ואלגוריתמים חדשים לחיסכון בהספק.

הגרסה החדשה משמשת לתכנון מעבד בינה מלאכותית

חברת הסטארט-אפ הבריטית Graphcore, המפתחת מעבד בינה מלאכותית, אימצה את IC Compiler II כפלטפורמת המימוש לתכנון השבב הראשון של החברה שלה: מעבד machine learning ביל שטח סיליקון גדול מאד. "אנחנו מתכננים מעבד מסוג חדש לחלוטין הבנוי מיחידת עיבוד אינטליגנטית (IPU) שמיועדת לעזור ללקוחות להאיץ את הפיתוח של מוצרי ושירותי בינה מלאכותית", אמר סיימון נוולס, ה-CTO של Graphcore. "יש לנו תכנון בהיקף גדול ביותר שנבנה מאפס, ולכן איכות תוצאות מהירה וניתנת לחיזוי לאורך כל שלבי התכנון שלנו היא מפתח להצלחה שלנו. אנחנו מאמינים שהתשתית החזקה והטכנולוגיות של IC Compiler II יאפשרו לנו להשיג את המטרות ולהביא את המוצר שלנו לשוק בזמן".

הגרסה החדשה של IC Compiler II מספקת טכנולוגיות המיועדות באופן ספציפי לשיפור איכות התוצאות (QoR), הזמן לתוצאות (TTR) והיכולת לאפשר ייצור בטכנולוגיות מתקדמות וזעירות. החברה שיפרה אופטימיזציית CCD – Clock and Data, באמצעות מנוע חדש בעל יכולות multi-objective, המסוגל ליצור איזון בין מדדי התזמון, השטח וצריכת ההספק, תוך השפעה מזערית על זמן הריצה. ה-CCD השתפר בזכות טכנולוגיות חדשות הממוקדות בצמצום צריכת ההספק.

חבילה של טכנולוגיות אופטימיזציה חדשות

טכנולוגיות אופטימיזציה אחרות שולבו בשלבים שלפני החיווט (pre-route) ובשלבים שאחרי החיווט (post-route) של התכנון. במהלך ה-pre-route, אופטימיזציה משופרת מבוססת global route מספקת שיפור ניכר בקורלציה בין תוצאות ה-pre-route לתוצאות ה-post-route, וכן מדדי QoR טובים יותר. בנוסף, אלגוריתם חזק ומתקדם של buffering עבור high fanout nets משפר את איכות התוצאות ברוב התכנונים המאתגרים. בשלב ה-post-route, שופר אלגוריתם האופטימיזציה באמצעות שתי טכנולוגיות חדשות: אופטימיזציה המונעת על-ידי אלגוריתם PBA – Path Based Analysis, ושיפורים באופטימיזציה המצמצמים זליגת הספק (leakage power).

בנוסף לאיכות התוצאות, הוכנסו לשימוש כמה טכנולוגיות חדשות במטרה להאיץ את זמני הריצה. לדוגמה, אלגוריתם ה-automatic placement clustering מספק מיקומים התחלתיים חכמים יותר המובילים לצמצום הצורך בריצות מצטברות נוספות. כתוצאה מכך, הוא מקצר את הזמן הנדרש להשגת placement אופטימלי. דוגמא אחרת היא טכנולוגיית automatic max density שמגדירה אוטומטית את צפיפות ופיזור התאים במהלך ה-placement, מה שמספק רמה אופטימלית של אורך החוטים, תזמון (timing) וקלות החיווט (congestion).

"ה-IC Compiler II ביסס את עצמו במהירות כפתרון ה-place and route הנבחר עבור תכנונים עתירי ביצועים", אמר ססין גאזי (Sassine Ghazi), סגן נשיא בכיר ומנכ"ל משותף של ה-Design Group בסינופסיס. "האימוץ האחרון על-ידי סטארט-אפ חדשני כמו Graphcore מדגים את המגמה הזו".

פורסם בקטגוריות: רכיבים ופתרונות אלקטרוניים