אינטל נערכת לייצור ב-2 ננומטר ב-2024

17 דצמבר, 2023

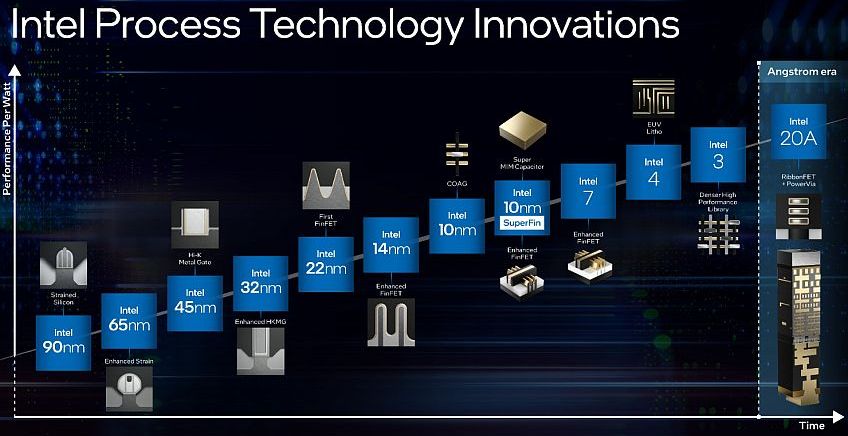

במחצית 2024 היא תתחיל לייצר רכיבים בתהליך החדש Intel 20A, אשר יתבסס על מסיכות EUV המאפיינות מימדים זעירים, על טרנזיסטורי RibbonFET החדשים ועל מארג המוליכים PowerVia

אחת מהמטרות המרכזיות של אסטרטגיית IDM 0.2 של חברת אינטל היא להדביק את הפער הטכנולוגי שנו צר בינה לבין סמסונג ו-TSMC, ולחזור למעמד החברה המובילה בתחום טכנולוגיות ייצור השבבים. מספר הכרזות שבוצעו לאחרונה על-ידי אינטל עשויים ללמד שהיא מתקרבת לשלב הזה, במיוחד כאשר מדובר במערב לטכנולוגיות ייצור מתקדמות של פחות מ-5 ננומטר. בשבוע שעבר סיפר מנהל חטיבת פיתוח טכנולוגיות רכיבים באינטל, סנג'אי נאטארייאן בראיון לניקיי היפני, שבשנת 2024 אינטל תתחיל לייצר רכיבים בטכנולוגיית 20A שלדבריו שהיא שוות ערך לייצור ברוחב צומת של 2 ננומטר. "אינטל תחזור למעמדה הוותיק כחברה המובילה את תחום מיזעור השבבים", אמר.

מאחורי האמירה הזאת מסתתרת מציאות שנעשית מורכבת מיום ליום, המקשה על ההשוואה בין הטכנולוגיות של החברות המתחרות. סיבה אחת נעוצה בעובדה שאינטל הפסיקה לסווג את הטכנולוגיות שלה במדדים של רוחב הצומת, סיבה שנייה (הקשורה לראשונה) היא שככל שטכנולוגיות המיזעור מתקדמות, הביצועים הכוללים של השבב נעשים תלויים בגורמים אחרים מלבד רוחב הצומת, דוגמת הגיאומטריה של הטרנזיסטור הבודד, סוג המצע, צפיפות החיבורים החשמליים בין הטרנזיסטורים ועוד. כך למשל, בשנתיים האחרונות אינטל חזרה וטענה שטכנולוגיית 10 ננומטר שלה שהיא שוות ערך לטכנולוגיית 7 ננומטר של המתחרות, בדיוק בגלל הגורמים האלה.

גם ביחס לתהליך החדש Intel 20A, קיים בלבול מסויים. בחלק מהאתרים הטכנולוגיים בעולם התהליך מוגדר כ-5 ננומטר, בחלק 3 ננומטר ובחלק 2 ננומטר. גם אינטל עצמה לא מספקת מידע רב מאוד על התהליך הזה, שאמור להיכנס לייצור בתחילת 2024, אולם פרטים שונים סביבו עשויים ללמד שמדובר בתהליך של 2 ננומטר, או שלפחות יש לו "אפקט" של 2 ננומטר. זהו התהליך החמישי לאחר השגת אבן הדרך של 10 ננומטר, הוא יתבסס על ייצור באמצעות מסיכות EUV המאפיינות מימדים זעירים, על טרנזיסטורי RibbonFET החדשים ועל מארג המוליכים PowerVia.

מדובר בשני תהליכים נפרדים שכל אחד מהם מאפשר להקטין את הגודל ברוטו של השבב, להפחיית את צריכת ההספק ולהאיץ את הביצועים. טרנזיסטורי RibbonFET מבוססים על הגדלת שטח הצומת בלא להגדיל את הטרנזיסטור, באמצעות בניית "צומת צפה" שבה השער המבקר את פעולת הטרנזיסטור של הטרנזיסטור מקיף את הצומת מכל הכיוונים. באמצעות המבנה הזה ניתן להעביר גם מטענים קטנים מאוד במהירות גדולה בהרבה.

מבנה PowerVia מתאר גישה חדשה לקישוריות בין הטרנזיסטורים בשבב. כיום הטרנזיסטורים מיוצרים בשכבה התחתונה של השבב כאשר מעליה נבנה מארג של מוליכים חשמליים האחראים לאספקת הכוח לטרנזיסטורים ולניתוב האותות ביניהם. בטכנולוגיית PowerVia מפרידים בין שכבת אספקת הכוח לשכבת הנתונים. בשיטה החדשה, שכבת הטרנזיסטורים נמצאת במרכז השבב, כאשר מארג אספקת הכוח נמצא בחלקו התחתון של השבב (קרוב אל המעגל המודפס), מארג המוליכים האחראים על ניתוב האותות בין הטרנזיסטורים נמצא בחלקו העליון של השבב. הדבר מקטין את תקורת הסיליקון מסביב לטרנזיסטור, ומגדיל את החסכוניות והמהירות של המעגל.

פורסם בקטגוריות: חדשות , סמיקונדקטורס