השלב הבא בפיתוח שבבים תלת-מימדיים אמיתיים

22 דצמבר, 2015

מיוחד ל-Techtime. מכון המחקר האירופי imec מפתח טכנולוגיות ייצור חדשות לשבבים תלת-מימדיים. בהן: חיבור פיסות סיליקון ברמת דיוק של 200 ננומטר

מיוחד ל-Techtime. מכון המחקר האירופי imec מפתח טכנולוגיות ייצור חדשות לשבבים תלת-מימדיים. בהן: חיבור פיסות סיליקון ברמת דיוק של 200 ננומטר

מאת: ד"ר אריק ביין, מנהל תוכנית 3D Integration ב-imec

בשנתיים-שלוש האחרונות חלה התפתחות טכנית וכלכלית רבה בהבנת מפת הדרכים הדרושה לפיתוח רכיבים תלת-מימדיים (3D-IC). ברמת הייצור הפלנרי הקונבנציונלי (2C) פותחו בתקופה הזו טכניקות ייצור המאפשרות לייצר קישורים קטנים מאוד בין המעגלים.

טכניקות אלה מכינות את הקרקע לקראת השילב התלת-מימדי בתעשיית השבבים, שהוא חיוני כדי שנוכל להמשיך ולשמור על התקפות של חוק מור.

אפשר לומר שרכיבי ה-3D הראשונים שנכנסו לתעשייה הופיעו במארזים הכוללים בעיקר שבבי זיכרון מסוג DRAM.

מערכות הטרוגניות במארז

הם נבנו בתצורה של פיסות סיליקון המונחות אחת על גבי השנייה ולכן קיבלו את הכינוי 3D stacked ICs. אנחנו צופים שהטכניקה הזו תמשיך להתפתח ובשנים הקרובות נראה מערכות הטרוגניות בתצורת stacked מסוג 3D SoCs. הכוונה למארזים שבהם מצויים שבבים מסוגים שונים, הבנויים בטכנולוגיות שונות, המנוחים זה על זה בצפיפות רבה מאוד. תחשבו לדוגמא על חיישן תמונה שמחוברים אליו מעגלי עיבוד ברמת הפיקסל הבודד.

צעד אחר שייעשה בעתיד הקרוב הוא בתחום של רכיבי 3D-IC: במקום לחבר פיסות סיליקון אחת לשנייה, יהיו שכבות מוערמות של טרנזיסטורים. הרעיון הזה נמצא בשלבי פיתוח ראשונים במעבדות רבות, והדוגמא הראשונה לאפשרויות הטמונות ברעיון הזה מומחשת על-ידי שבבי הזיכרון 3D-NAND, שבהם מוערמים תאי הזיכרון אחד על גבי השני, לעתים אפילו 50 תאים כאלה, כשהם מקושרים אל המערך באמצעות ערוץ הבנוי מטרנזיסטור אחד בלבד.

שני האתגרים המרכזיים: הערמה וקישוריות

מכיוון שהוא אחד מהאתגרים הטכנולוגיים החשובים ביותר הניצבים כיום לפנינו, התחלנו ב-imec לעבוד על שיפור רמת הצפיפות של מרכיב הקישוריות (interconnectios) בתוך שבבים תלת-מימדיים. הדבר פותח אפשרויות חדשות. במקום להסתפק בקישוריות בין בלוקים פונקציונליים נפרדים, נוכל לרדת לרמות נמוכות בהרבה של תת-מעגלים זעירים. למשל: קישור מעבדים בסיסיים וקטנים לכל פיקסל בחיישן, או לכל תא בזיכרון.

היכולת הזו היא חיונית כדי לספק את הרכיבים שיידרשו למעבדי העתיד, אבזרי המולטימדיה, חיישנים ברזולוציה גבוהה ועוד. אולם כדי לממש את הרעיון יש צורך בטכניקות הערמה וקישור מדוייקות יותר. זהו אחד מהתחומים המרכזיים שבו מתעסקת כיום קבוצת 3D integration ב-imec ביחד עם השותפים שלנו.

השנה הצלחנו להתקדם בכיוון הזה מצורה משמעותית, גם בקישוריות בין פיסת הסיליקון למצע הפרוסה (die-to-wafer) וגם ברמת הקישוריות בין מצע למצע (wafer-to-wafer stacking). שתי הדרכים העיקריות להערים שבבים ולייצר ביניהם קישוריות חשמלית.

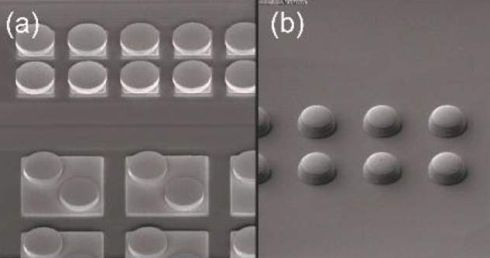

בהערמת פיסה על מצע, שבבים מוכנים מודבקים על מצע שעבר עיבוד. התקן הממוצע בתעשייה לקישוריות מהסוג הזה היא מירווחים של 40um. אבל בניסויים שביצענו הצלחנו להגיע למירווחים של 10 מיקרון, חמישה מיקרון ואפילו 3 מיקרון.

האתגר הוא לייצר אותם במהירות, בדייקנות וברמת תפוקה כלכלית. פיתחנו תהליך לייצור מגעים זעירים (micro-bumps) בתהליך thermo-compression הנעזר בכלי יציור חדשים ומדוייקים מאוד.

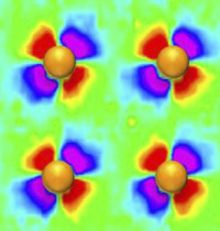

להערמת מצע על מצע, המטרה היא לקשר בין שכבות סיליקון דקות מאוד (לאחר שיוף) ברמת דיוק של 200 ננומטר. אחד מהקשיים הובלטים ביתוח התהליך קשור לאופן שבו מתנהגות שתי פרוסות סיליקון מאוד חלקות. הן נוטות להיכרך אחת מסביב לשנייה ולייצר עיוותים בסדר גודל של רמת הדיוק שאליה אנחנו צריכים להגיע. כרגע אנחנו מחפשים פתרון לבעיה הזו.

כדי לבצע הצמדה וחיבורים חשמליים בין המצעים, אנחנו עובדים בשני נתיבים במקביל. הראשון מבוסס על הצמדת silicon-carbon-nitride וחיבוריות חשמלית מסוג through-silicon vias. בשיטה הזו אנחנו מתכננים לשייף את המצע העליון לעובי של חמישה מיקרון ולייצר מעברי TSV בקוטר של 1 מיקרון.

השיטה השנייה נקראת hybrid bonding. גם כאן אנחנו משתמשים בסיליקון-קרבון-ניטריד (SiCN) להצמדה הפיסית, אולם מייצרים את המגעים החשמליים באמצעות דפנות נחושת מאוד דקות (5 ננומטר). הדבר מאפשר להגיע למירווחים של 3.6um, ואף יותר – בחלק מהניסויים הצלחנו להגיע לגודל של 1.8um.

אודות המחבר: ד"ר אריק ביין מנהל את תוכנית המארזים המתקדמים במכון המחקר imec. הצוות שלו עוסק בפיתוח מארזים ושיטות קישוריות צפופות מאוד עבור רכיבי system-in-a-package, מארזים ברמת הסיליקון, מארזים לרכיבי RF, רכיבי RF-MEMS ועוד.

ראו גם: imec Technology Forum Israel 2016

למידע נוסף:

> Lightning-fast die to wafer stacking

> Exploring graphene on the interconnect test bench

> Polariscopy reveals TSV stress fields

> A novel approach for integrating ultralow-k dielectrics

> Imec compares yield of two major flavors of chip stacking

> When will we find 3D chips in our smartphones?

פורסם בקטגוריות: חדשות , סמיקונדקטורס

פורסם בתגיות: featured