חוק מור עובר מרמת הטרנזיסטור אל מארזי השבבים

4 ינואר, 2016

הלחץ של יצרני הסמארטפונים דוחף את תעשיית מארזי השבבים לשנות את פניה. כבר היום כשליש מהרכיבים בסמארטפונים המובילים בשוק מופיעים בתוך מארזי WLP סופר-צפופים

הלחץ של יצרני הסמארטפונים דוחף את תעשיית מארזי השבבים לשנות את פניה: כשליש מהרכיבים בסמארטפונים המובילים מופיעים בתוך מארזי WLP סופר-צפופים

למרות שהתעשייה מתמודדת עם האטה בתהליך מיזעור הטרנזיסטורים שתואר בחוק מור, הצורך של יצרני המערכות ברכיבים צפופים ועתירי פונקציונליות אינו פוחת. במיוחד הדבר בולט בתעשיית הטלפונים הסלולריים, אשר בעקבות האטת חוק מור, דוחפת להתפתחות מהפיכה אלטרנטיבית ברמת מארזי השבבים.

הצורך של היצרנים לספק מכשירים דקים מאוד ובעלי פונקציונליות מלאה מייצר מהפיכה באופן שבו נארזים היום שבבים ונמסרים ללקוחות. אחת מהתופעות האלה מתבטאת בגידול המהיר בשימוש במארז WL-CSP, שזהו קיצור של Wafer Level Chip Scale Packages.

במארזים אלה מייצרים את כדורי הבדיל על-פני פיסת הסיליקון כבר בשלב הייצור בפאב, עוד לפני ניסור פרוסת הסיליקון לפיסות נפרדות. להערכת חברת המחקר ASE Group, כ-30% מהשבבים בסמארטפונים כיום מיוצרים במארזי WL-CSP, שבהם כדורי הבדיל ממוקמים ישירות מתחת לפיסת הסיליקון.

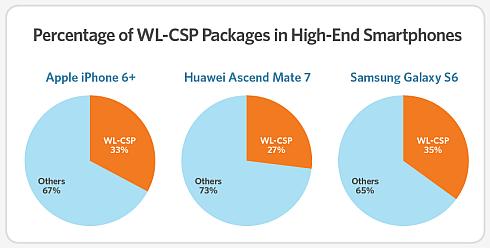

כך למשל, מכשיר האייפון הראשון של אפל משנת 2007 כלל רק שני רכיבים במארז WL-CSP, ואילו המכשיר איפיון 6 כולל כבר 26 רכיבים במארז הזה. חברת Yole Developement בדקה שלושה דגמים מובילים וגילתה דמיון רב ביניהם: 27% מהשבבים במכשיר Ascend Mate 7 של וואווי הסינית מופיעים במארזי WL-CSP. אפל מקדימה אותה במקצת עם 33% מהרכיבים באייפון 6, והמובילה היא סמסונג עם 35% מהרכיבים במכשיר Galaxy S6.

מסורתית, מארזי WLP יועדו לשימוש ברכיבים שבהם יש פיסת סילקון קטנה מאוד עם מספר קטן של מגעים חיצוניים. אולם הסמארטפונים שינו את התמונה, ולהערכת TechSearch המגמה היום היא של גידול שנתי בשיעור של 9% בשנה בשימוש במארזי WLP.

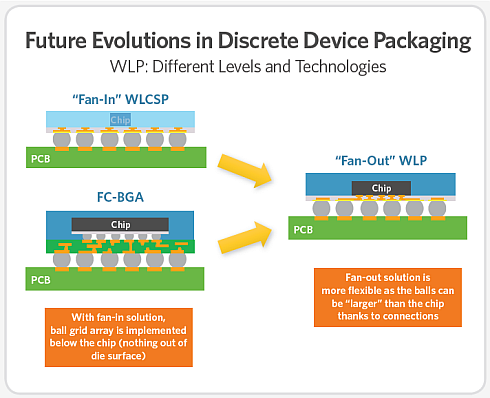

כעת גובר השימוש במארזים ברמת השבב מהסוג Fan-out Wafer Scale Packaging. במארזים האלה מונחת פיסת הסיליקון על-גבי פיסת סיליקון אחרת, גדולה ממנה רק במקצת, אשר בצד השני שלה מונחים כדורי הבדיל המתחברים למעגל המודפס.

חלק מהמומחים סבור שהמארזים האלה יבטלו את הצורך במארזי 3D המורכבים הנמצאים היום בשימוש ברכיבים גדולים, שבהם מוצבות מספר פיסות סיליקון על גבי מצע מורכב המקשר ביניהן לבין המעגל המודפס באמצעות מוליכים אנכיים (Through Silicon Vias). טכניקה זו נחשבת ליקרה וקשה יותר לביצוע.

מארזי Fan-out כבר כוללים קטגוריית מארז צפוף במיוחד (HD-FO), שבה רוחב המוליכים והמרווחים שביניהם מגיע לכ-10 ננומטר. מנהל פיתוח אסטרטגי לנושא טכנולוגיות חדשות בחברת Applied Materials, מייק רוסה, אמר שהחברה מפתחת כעת פתרונות לתחום המארזים המתקדמים במטרה למזער אותם.

"אחד מהאתגרים המרכזיים בטיפול בפרוסות סיליקון צפופות ודקות יותר, הוא החיתוך שלהן. המרווחים בין פיסות הסיליקון בתוך הפרוסה נעשים צרים מאוד, וכל שבר שנוצר בתהליך החיתוך שלהן, פוגע בפונקציונליות של הרכיב המוגמר".

אולם התוצאה המרכזית של התהליך היא שייצור המארז מתקב במהירות אל רמת הפאב שבה מיוצר הסיליקון עצמו. "הקו המפריד בין ייצור הסיליקון (Front-end) לבין תשתית המוליכים החשמליים שלו (Back-end), נעשה מטושטש".

ניתן לחוש במגמה הזו כאשר נכנסים לקו הייצור של מפעל מארזים מודרני (OSAT). בעבר התבסס קו הייצור על מכונות חיבור חוטים, מכונות חיתוך, הצמדה והדבקה. כיום מפעלים רבים מזכירים מפעלי ייצור שבבים וכוללים ציוד ייצור דומה.

למידע נוסף בנושא: מגזין NanoChip של חברת Applied Materials

פורסם בקטגוריות: חדשות , סמיקונדקטורס , רכיבים

פורסם בתגיות: featured