אינטל הכריזה על FPGA ייעודי להאצת חישובים

20 דצמבר, 2017

רכיב Stratix 10 MX FPGA שהוכרז השבוע, חונך את טכנולוגיית המארזים 3D SiP החדשה, המאפשרת להרכיב ברכיב יחיד מעבדי CPU, מערכי FPGA, מגדלי זיכרון ומקמ"שים מהירים

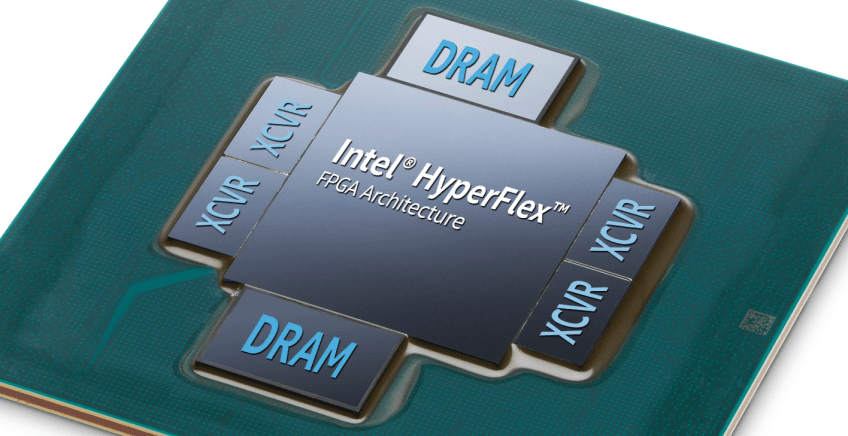

חברת אינטל הכריזה על רכיב FPGA חדש מדגם Stratix 10 MX FPGA המותאם במיוחד להאצת ביצועים במרכזים עתירי מיחשוב. מדובר ברכיב המיתכנת הראשון בתעשייה המצוייד בזיכרון HBM2 מהיר (High Bandwidth Memory DRAM). להערכת אינטל, השילוב של זיכרון HBM2 מאפשר לרכיב המיתכנת להגדיל פי 10 את רוחב הפס של התקשורת עם הזיכרון בהשוואה לפתרון הכולל רכיב DDR נפרד. הדבר מאפשר לייעד את הרכיב החדש למטלות האצת עיבוד במערכות עתירות עיבוד (HPC), מרכזי נתונים, משימות וירטואליזציה של פונקציות רשת (NFV) ויישומים הדורשים העברה מהירה של קבצים גדולים מאוד.

ה-CPU נותר מובטל

בסביבות עתירות עיבוד יש חשיבות גדולה מאוד בכיווץ ופריסת נתונים לפני או אחרי העברת הקבצים הגדולים. השילוב של FPGA עם זכרון HBM2 מאפשר לפרוס ולכווץ קבצים וגם להעביר אותם במהירות גדולות יותר. הרכיב החדש מותאם לשימוש גם בסביבה שבה מתבצע ניתוח מידע בכמויות גדולות (High Performance Data Analytics), שבה יש צורך בהאצת חומרה בזמן אמת. זאת באמצעות היכולת שלו לבצע בו-זמנית כתיבה/קריאה והצפנה/פיענוח, מבלי להישען על משאבי ה-CPU.

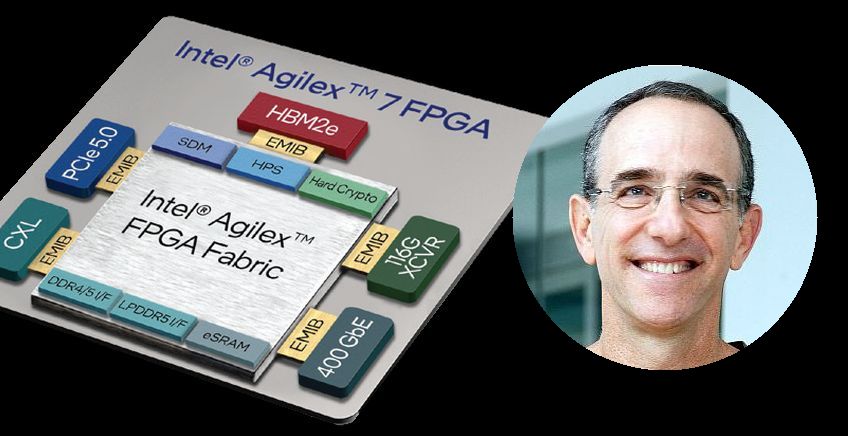

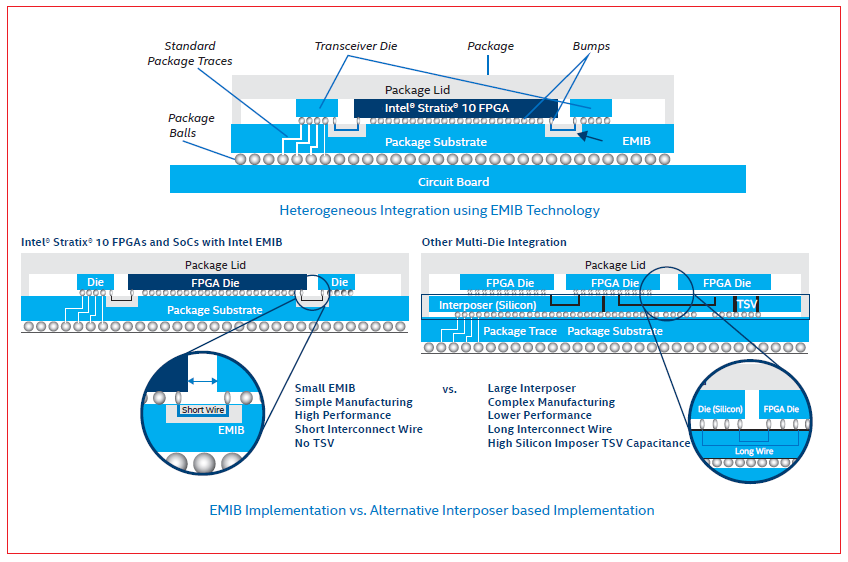

הרכיב החדש מספק קצב תקשורת עם הזיכרון המגיע למהירות של עד 512GB לשניה. הוא מיוצר במארז SiP – System-in-Package מורכב הכולל זכרונות DRAM המונחים אחד על השני בתצורת מגדל (Stacked) ומחוברים באמצעות מעברי TSV. הם יושבים על מצע המתחבר באמצעות מגעי Micro bumps צפופים אל מערך FPGA הפועל בתדר של 1GHz. הרכיב כולל גם ערוץ תקשורת פנימי מסוג Embedded Multi-Die Interconnect Bridge – EMIB, המקשר בין ה-FPGA ובין המקמ"שים כדי להאיץ את התקשורת בין הזיכרון ל-FPGA. אינטל מייצרת את ליבת ה-FPGA מטרנזיסטורי FinFET בתהליך של 14 ננומטר.

מארזים חדשים מסוג 3D SiP

הרכיב חונך את טכנולוגיית האריזה החדשה של אינטל, 3D SiP המאפשרת לשלב מספר שבבים במארז יחיד מסוג SiP – System-in-Package, גם כשהם מונחים בתצורה אנכית, אחד על-גבי השני. הטכנולוגיה הזו מאפשרת לשלב ברכיב יחיד מגוון גדול של טכנולוגיות שונות: זיכרונות, CPU, ASIC, רכיבי קישוריות ומקמ"שים שיוצרו בנפרד בתהליכי ייצור אחרים מאלה של המעבדים וה-FPGA. להערכת אינטל, המארז החדש מאפשר לספק בעתיד מקמ"שים בעלי מהירות תקשורת של עד 56Gbps. כעת מכיל Stratix 10 קישוריות PCIe Gen3, אולם בעתיד ניתן יהיה לשלב בו מודולי תקשורת אחרים, דוגמת איתרנט מרובה פורטים, PCIe Gen4 ואפילו מודולי תקשורת אופטיים.

הרכיב חונך את טכנולוגיית האריזה החדשה של אינטל, 3D SiP המאפשרת לשלב מספר שבבים במארז יחיד מסוג SiP – System-in-Package, גם כשהם מונחים בתצורה אנכית, אחד על-גבי השני. הטכנולוגיה הזו מאפשרת לשלב ברכיב יחיד מגוון גדול של טכנולוגיות שונות: זיכרונות, CPU, ASIC, רכיבי קישוריות ומקמ"שים שיוצרו בנפרד בתהליכי ייצור אחרים מאלה של המעבדים וה-FPGA. להערכת אינטל, המארז החדש מאפשר לספק בעתיד מקמ"שים בעלי מהירות תקשורת של עד 56Gbps. כעת מכיל Stratix 10 קישוריות PCIe Gen3, אולם בעתיד ניתן יהיה לשלב בו מודולי תקשורת אחרים, דוגמת איתרנט מרובה פורטים, PCIe Gen4 ואפילו מודולי תקשורת אופטיים.

למידע נוסף: Stratix® 10 MX FPGA

פורסם בקטגוריות: FPGA , חדשות , סמיקונדקטורס