סינופסיס הכריזה על ערכת פיתוח ליישומי ראייה מלאכותית

4 נובמבר, 2018

להערכת החברה, ערכת DesignWare HPC מאפשרת להשיג הפחתה של 39% בצריכת ההספק, צמצום של 10% בשטח או שיפור של 7% בביצועים של SoC הכולל רשתות נוירוניות (CNN)

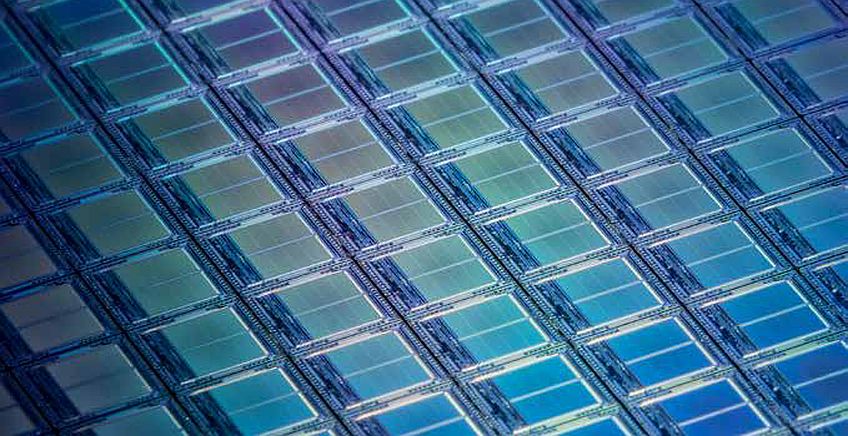

חברת סינופסיס (Synopsys) הכריזה על ערכת הפיתוח DesignWare High Performance Core – HPC עבור מעבדי EV6x שנועשה לסייע למתכננים לעמוד בדרישות הביצועים, ההספק והשטח של מערכות על-גבי שבב (SoC) ביישומי ראייה משובצת (EV) ובינה מלאכותית (AI). הערכה DesignWare HPC כוללת חבילה של שבבי זיכרון במהירות גבוהה ושל ספריות לוגיות בעלות ייעודיות, במטרה לבצע אופטמיזיצה של יחידות העיבוד vector DSP ומנועי הרשת הנוירונית (Convolutional Neural Network) הכלולים במעבד EV6x.

להערכת החברה, הערכה מאפשרת להשיג הפחתה של 39% בצריכת ההספק, צמצום של 10% בשטח או שיפור של 7% בביצועים של ה-SoC. הערכה כוללת מימושים של יחידות זיכרון מטמון מהירים SRAM בעלי שתי יציאות תקשורת וחבילה של תאים לוגיים הכוללים multi-bit flip-flops, וכן דוחסים ומרבבים. קיימות אפשרויות זמינות גם עבור תהליך overdrive או מתח נמוך, PVT – Process, Voltage, Temprature, תאים מרובי ערוצים, בדיקות עצמיות ותיקון עצמי של הזכרונות (BIST – Built-In Self Test).

הערכה מספקת תסריטים (scripts) של זרימת תכנון (design flow) וייעוץ של מומחים בנוגע למיטוב ליבות, כולל שירותי מימוש FastOpt. "ל-IP הפיזי בו משתמשים לצורך מימוש של מעבדים בתוך מערכות חכמות יש השפעה משמעותית על הביצועים, צריכת ההספק והשטח של התכנון", אמר ג'ון קוטר, סגן נשיא לשיווק IP בסינופסיס. "השילוב בין ערכת הפיתוח DesignWare HPC ומעבדי הראייה EV6x מאפשר למתכננים למטב את הליבות שלהם עבור כל טווח המהירויות, ההספקים והשטחים הנדרשים בכדי לעמוד בדרישות היחודיות של המערכות על גבי שבב שלהם".

זמינות

ערכת הפיתוח DesignWare HPC מותאמת לרכיבים המיוצרים בטכנולוגיית FinFET בגיאומטריה של 7ננו-מטר, 12 ננו-מטר ו-16 ננו-מטר היא זמינה כעת.

פורסם בקטגוריות: חדשות , סמיקונדקטורס , תוכנה ותכנון אלקטרוני

פורסם בתגיות: סינופסיס