ביום ג' ה-19 במאי 2026 בשעה 19:00 לפי שעון ישראל, חברת סינופסיס (Synopsys) וובינר משותף עם חברת אינטל (Intel) אשר יוקדש לסוגיית הבדיקות הסופיות (Signoff) של שבבים תלת-מימדיים (3DIC) המבוססים על ארכיטקטורה ריבוי אריחים (Disaggregated Designs), הכוללת Chiplets ו/או פיסות סיליקון נפרדות מסוגים שונים. הוובינר יועבר על-ידי מהנדסת בכירה באינטל, ויקטוריה קולסוב (Victoria Kolesov).

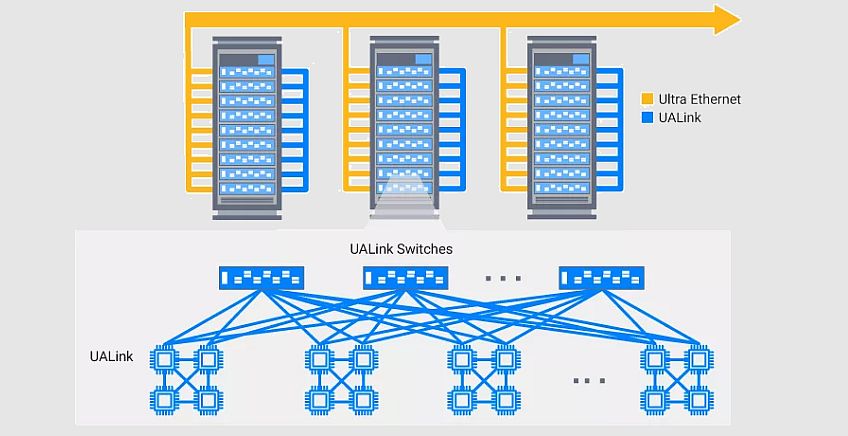

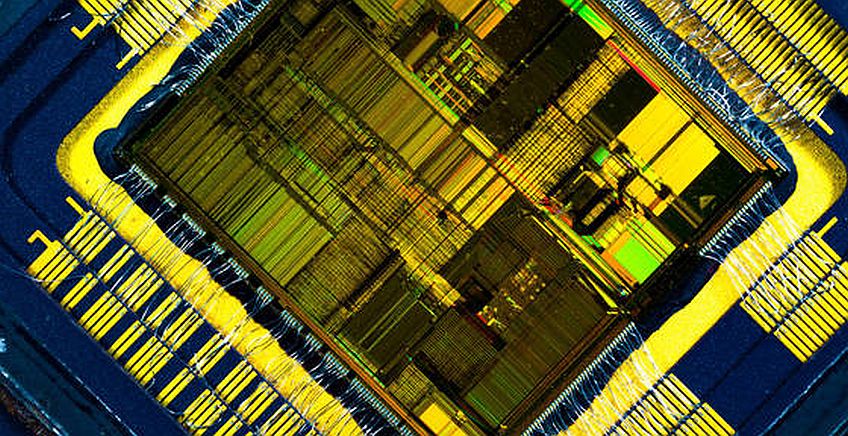

במסגרת הוובינר בשם From Construction to Signoff: 3DIC Methodology for Disaggregated Designs, תציג אינטל כיצד התכנונים המפורקים שלה (Disaggregated Designs) בפלטפורמות לקוח ושרת הובילו להתפתחות מתודולוגיות חדשות לבניית מערכות 3D מרובות־שבבים (Multi-Die) וביצוע ה-Signoff שלהן. היא תציג ניסיון מעשי בשימוש בזרימות העבודה המלאות של סינופסיס, כולל: Signoff לניתוח תזמונים סטטי (Static Timing Analysis), ואימות פריסה תלת־ממדית (3D Layout Verification) בתכנוני Interposer פסיביים ו-Interposer אקטיביים.

במסגרת הוובינר בשם From Construction to Signoff: 3DIC Methodology for Disaggregated Designs, תציג אינטל כיצד התכנונים המפורקים שלה (Disaggregated Designs) בפלטפורמות לקוח ושרת הובילו להתפתחות מתודולוגיות חדשות לבניית מערכות 3D מרובות־שבבים (Multi-Die) וביצוע ה-Signoff שלהן. היא תציג ניסיון מעשי בשימוש בזרימות העבודה המלאות של סינופסיס, כולל: Signoff לניתוח תזמונים סטטי (Static Timing Analysis), ואימות פריסה תלת־ממדית (3D Layout Verification) בתכנוני Interposer פסיביים ו-Interposer אקטיביים.

What you’ll learn:

- How Intel approaches 3DIC construction for disaggregated designs

- Key requirements for static timing and layout signoff in 3DIC flows

- Differences between passive and active interposer signoff considerations

- How accuracy requirements influence 3D construction methodologies

- Best practices for achieving correct‑by‑construction 3DIC signoff.

Victoria Kolesov joined Intel in 2001 and has held a variety of responsibilities including RTL development, design completion, and design automation. Her current focus is interconnect implementation and 3D design integration. Victoria obtained her MS in Computer Science from St.Petersburg Technical University, Russia.

למידע נוסף ורישום:

3DIC Methodology for Disaggregated Designs

As power integrity challenges increase with advanced nodes and multi-die architectures, EMIR analysis must evolve beyond traditional signoff. In this Synopsys webinar, we will show how RedHawk-SC is expanding its capabilities not only to enhance EMIR analysis, but also to enable IR-aware Static Timing Analysis (IR-STA) and IR-driven ECO (IR-ECO) flows.

As power integrity challenges increase with advanced nodes and multi-die architectures, EMIR analysis must evolve beyond traditional signoff. In this Synopsys webinar, we will show how RedHawk-SC is expanding its capabilities not only to enhance EMIR analysis, but also to enable IR-aware Static Timing Analysis (IR-STA) and IR-driven ECO (IR-ECO) flows.

Speaker: Diwakar Kumaraswamy, Technical Product Manager at Synopsys with over 15 years of experience in SoC design and high-speed interconnects. He specializes in PCIe architecture for AI and HPC, supporting next-generation connectivity solutions for advanced infrastructure.

Speaker: Diwakar Kumaraswamy, Technical Product Manager at Synopsys with over 15 years of experience in SoC design and high-speed interconnects. He specializes in PCIe architecture for AI and HPC, supporting next-generation connectivity solutions for advanced infrastructure.

Key benefits of migrating to PCIe 5.0

Key benefits of migrating to PCIe 5.0

Speaker: Jim Schultz, senior staff product manager for the Synopsys EDA Group. He holds a B.S. in electrical engineering from the University of California, Davis with an emphasis in electromagnetics. His design engineering experience includes physical verification, design planning and design implementation on CPUs, networking and security chips. As a product engineer, he has supported design implementation, design planning and package design at various EDA companies.

Speaker: Jim Schultz, senior staff product manager for the Synopsys EDA Group. He holds a B.S. in electrical engineering from the University of California, Davis with an emphasis in electromagnetics. His design engineering experience includes physical verification, design planning and design implementation on CPUs, networking and security chips. As a product engineer, he has supported design implementation, design planning and package design at various EDA companies.