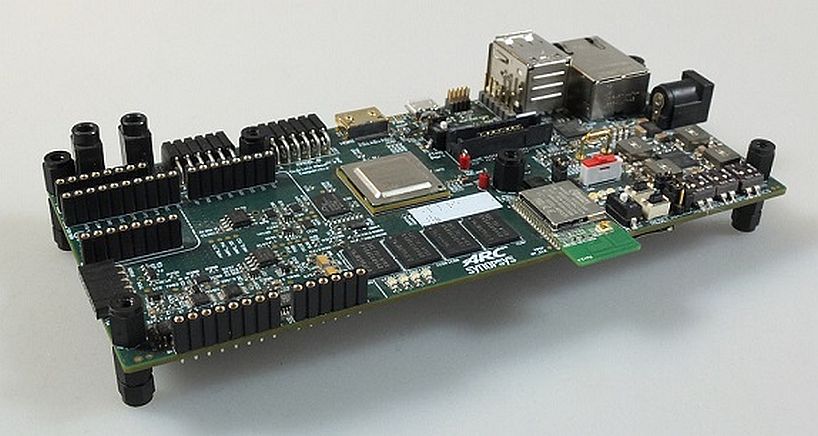

בתמונה למעלה: ערכת פיתוח למעבדי ARC HS

חברת סינופסיס הכריזה על משפחה חדשה של מעבדים ממשפחת ARC מרובי ליבות. המעבדים החדשים מופיעים במתכונת של קניין רוחני (IP) במסגרת ספריית הקניין הרוחני DesignWare של החברה. ההכרזה כוללת את מעבדי ARC HS5x בעלי 32 סיביות ומעבדי ARC HS6x בעלי 64 ביט. הם מבוססים על ארכיטקטורת ISA החדשה, ARCv3. כאשר מייצרים אותם בתהליך של 16 ננומטר הם מספקים עוצמת עיבוד של עד 8,750DMIPS לליבה.

בגרסא מרובת הליבות, מעבדי ARC HS החדשים כוללים מארג קישוריות פנימי (interconnect) המקשר עד 12 ליבות ותומך בממשקים המתחברים אל עד 16 מאיצי חומרה. הם נתמכים בידי ערכת הפיתוח ARC MetaWare, המחוללת קוד יעיל. הם מיועדים לשימוש בכונני SSD, מערכות בקרה, מערכות מידע ובידור בכלי רכב, תחנות בסיס אלחוטיות, מערכות בקרה אלחוטית ונתבי רישות ביתיים. המעבדים תומכים בפעולות וקטוריות של F16, F32 ו-F64 עם שיהוי צבירה של עד שני מחזורי שעון.

כמו כל מעבדי ARC, גם הם ניתנים להגדרת תצורה ומממשים טכנולוגיית ARC Processor Extension, המספקת תמיכה בהוראות תפורות וייעודיות עבור הצרכים הייחודיים של כל יישום. "יישומים משובצים כמו SSDs, בקרה אלחוטית ורשתות ביתיות הופכים ליותר ויותר מורכבים ודורשים שיפורים ניכרים בביצועים במסגרת תקציבי צריכת הספק ושטח מוגבלים", אמר ג'ון קוטר, סגן נשיא בכיר לשיווק ואסטרטגיית IP בסינופסיס.

"היציאה לשוק של ה-ARCv3 ISA החדש וההשקה של מעבדי ARC HS5x ו-HS6x, מאפשרים למתכננים להתמודד עם דרישות הביצועים הגוברות עבור התכנונים המשובצים שלהם היום ובעתיד". מעבדי ה-DesignWare ARC HS5x ו-HS6x מתוכננים להיות זמינים ברבעון השלישי של 2020. המעבדים החדשים יכללו את ה-ARC HS56, HS57D, HS58, HS66, HS68 וגרסאות מרובות ליבות (HS56MP, HS57DMP, HS58MP, HS66MP, HS68MP) של כל אחד מהמעבדים.