בתמונה למעלה: הדמייה תלת-מימדית של טרנזיסטור SuperFin החדש

חברת אינטל הוציאה מהשרוול קלף חדש ומפתיע שנועד להחזיר אותה אל ההובלה בתחום תהליכי הייצור, לאחר שסמסונג ו-TSMC הקדימו אותה במירוץ לייצור שבבים בגיאומטריה של 7 ננומטר. במסגרת ארוע הטכנולוגיה השנתי, Architecture Day של החברה, שהתקיים ביום ה' האחרון, היא הכריזה על תהליך ייצור של טרנזיסטור תלת-מימדי מסוג חדש שקיבל את השם SuperFin.

אינטל מסרה שזהו השיפור הגדול ביותר בתוך אותו דור טכנולוגי שנעשה באינטל אי-פעם. הדור הראשון של הטרנזיסטורים החדשים נקרא 10nm SuperFin, וישמש לייצור המעבד החדש של החברה, Tiger Lake, שייצא לשוק בסוף השנה, לקראת עונת החגים. לטענת אינטל, טכנולוגיית 10nm SuperFin מקבילה לתהליך ייצור של 7 ננומטר במונחי צפיפות וביצועים.

אינטל נפרדת ממדד הננומטר

מכיוון שיש לדעתה בלבול גדול סביב המושג "ננומטר" והתהליכים החדשים שהחברות מציעות, היא החליטה להתנתק ממנו והמוצרים הבאים שלה בטכנולוגיית 10 ננומטר לא יכונו בשם המציין את רוחב הצומת. הם ייקראו SuperFin Technology, ובהמשך Enhanced SuperFin. אינטל צופה שאספקת מעבדי מחשבים בטכנולוגיית 7 ננומטר שלה תהיה בסוף 2022 או בתחילת 2023.

טכנולוגיית SuperFin מהווה שיפור של הטרנזיסטורים התלת-מימדיים המוכרים מסוג FineFET, שאינטל ייצרה אותם לראשונה בשנת 2012. בתהליך החדש היא ביצעה שינויים מבניים והוסיפה חומרים חדשים המשפרים את הביצועים של הטרנזיסטור ואת הביצועים של המעגל המוכלל כולו, הבנוי ממספר רב של טרנזיסטורי SuperFin.

החידושים המרכזיים: שיפור תהליך הבנייה של שכבות גבישיות על מגעי ה-Source וה-Drain של הטרנזיסטור מחזק את המבנה ומקטין את התנגדות הצומת למעבר זרם. בנוסף, היא ביצעה שינוי במבנה הצומת המאפשר להעביר כמות גדולה יותר של מטענים ובמהירות גדולה יותר מאשר בטרנזיסטורי FineFET. החידוש הטכנולוגי קשור גם לשבב כולו ולא רק לטרנזיסטור הבודד: תהליך ייצור המאפשר להקטין את עובי שכבות ההפרדה בתוך השבב מפחית ב-30% את ההתנגדות החשמלית של מוליכי המתכת (Via) המקשרים בין הטרנזיסטורים לבין שכבת ההולכה והקישוריות.

הטכנולוגיה החדשה כוללת שיטה חדשה לייצור קבלי MIM – Metal-Insualtor-Metal. לייצור קבלים במהלך בניית השבב יש תפקיד חשוב. טרנזיסטורים מסוג MOS למיניהם כוללים קבל בתוך המבנה הפנימי שלהם, והמעגלים הלוגיים כוללים קבלים נוספים מחוץ לטרנזיסטור. אלא שהקיבוליות שלהם (Capacitance) היא נמוכה מאוד, ולכן הביצועים מוגבלים. לכן הם גם גוזלים שטח גדול מאוד מהמעגל השלם. טכנולוגיית SuperFin כוללת שיטת ייצור קבלי MIM המבוססת על בניית מספר רב של שכבות מוליך-מבודד בעובי של אנגסטרמים בודדים, המגדילה פי חמישה את הקיבוליות שלהם.

מארזים תלת-מימדיים צפופים

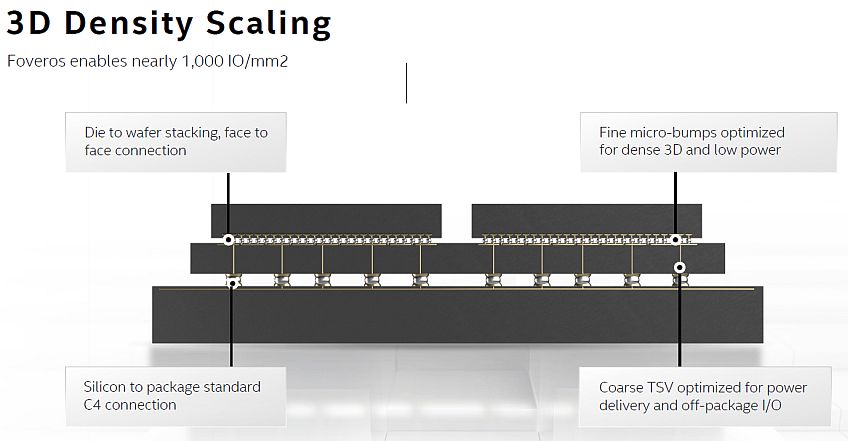

ביחד עם טכנולוגיית SuperFin, היא הכריזה על אסטרטגיה אגרסיבית בתחום המארזים המתקדמים. אינטל לומדת את התחום הזה כמעט 20 שנה, מאמץ שהביא לפיתוח טכנולוגיית EMIB המאפשרת לחבר מספר אריחי סיליקון בתוך מארז אחד, בצפיפות גבוהה מאוד. בסוף 2019 היא הוציאה לשוק רכיבי FPGA ממשפחת Agilex המבוססים על הטכנולוגיה החדשה. בשנת 2019 היא חשפה את טכנולוגיית Foveros לבניית רכיבים במתכונת תלת-מימדית: היא מבוססת על שכבת בסיס לוגית ראשונית, שעליה ניתן להתקין שכבות לוגיות נוספות, למשל רכיבי CPU או רכיבי FPGA, ועליהן שכבות נוספות כמו מעגל אנלוגי או זכרונות.

האריחים מקושרים באמצעות מגעים כדוריים זעירים (Micro-bumps) המקשרים את המודולים החשמליים של פיסות הסיליקון. לפני כחודשיים הטכנולוגיה הזאת נכנסה לראשונה אל השוק, כאשר אינטל הכריזה על מעבדי Intel Core i5 ו-i3 המבוססים על ליבת 10nm Sunny Cove שפותחה באינטל ישראל. הם מופיעים במארז תלת-מימדי הכולל מספר שבבים המסודרים בתצורת מגדל (Stack), המאפשרת לצמצם ביותר מ-50% את השטח שהמעבד תופס על-גבי הלוח המודפס (PCB).

לדברי הארכיטקט הראשי של החברה, ראג'ה קודורי, אינטל נמצאת רק בתחילת המסע לשיפור המארז, והיעד שלה הוא לפתח מארז צפוף במיוחד הכולל מגעים כדוריים זעירים המצויים במרחק של פחות מ-10 מיקרו-מטר אחד מהשני, ומגיעים לצפיפות של עד 10,000 מגעים במ"מ מרובע. בכך אינטל מחוייבת לאסטרטגיה של קודורי שנחשפה בשנת 2018, שלפיה מנוע הצמיחה של תעשיית השבבים אינו מצוי ברוחב הצומת של הטרנזיסטור, אלא בשילוב של ביצועים, אינטגרציה וארכיטקטורה.

השפעת הטכנולוגיה על המודל העסקי של אינטל

ראוי לציין שאסטרטגיית המארזים אינה רק מענה טכנולוגי למירוץ אחר גיאומטריות קטנות יותר שאותו אינטל אינה מובילה, אלא שהיא גם מספקת בסיס לרעיון עסקי חדש: מארזים מרובי-שבבים מאפשרים לאינטל לשלב בתוך המוצרים שלה פיסות סיליקון וטכנולוגיות שהובאו ממקורות מחוץ, ואפילו כאלה שיוצרו על-ידי חברות אחרות.

בכך ניתן להאיץ את קצב ההוצאה לשוק של מוצרים חדשים, לבנות אקוסיסטמס מסוג חדש סביב מוצריה – ולהתמקד ביכולות הליבה של החברה – בלא צורך לספק את הסביבה הכוללת של השבב. גם הרעיון הזה נבדק כעת באמצעות הניסוי של Agilex FPGA.

האזינו לשתיים מתוכניות הפודקאסט שלנו שבהן התארחו אנשים מאינטל:

"להמציא את האקסלרטור מחדש" עם צחי וייספלד, מנהל האקסלקטור Intel Ignite (עלה בחודש אוגוסט 2020)

"בינה מלאכותית באינטל" עם ד"ר אמתי ערמון (עלה בחודש מרץ 2020)