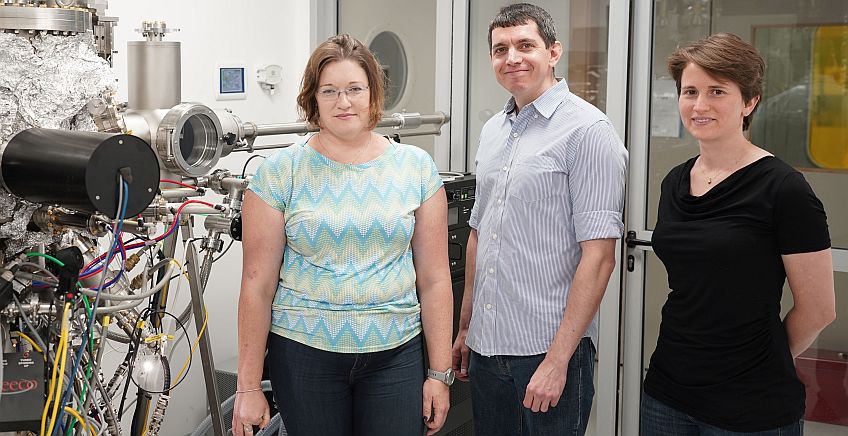

בתמונה למעלה מימין לשמאל: לישי שהם, פרופ' ליאור קורנבלום וד"ר מריה בסקין במעבדה. צילום : ניצן זוהר, דוברות הטכניון

חוקרים בפקולטה להנדסת חשמל ומחשבים בטכניון השיגו שליטה על חומר חדש שעשוי להערכתם להחליף בעתיד את הסיליקון כחומר היסוד בייצור רכיבים אלקטרוניים. מטרת המחקר היא למצוא חומרים המאפשרים להמשיך ולמזער את הרכיבים האלקטרוניים. במאמר שפורסם בכתב העת המדעי Advanced Functional Materials, הם הציג צוות חוקרים בראשות פרופ' ליאור קורנבלום, יכולת שליטה במבנה ובתכונות החשמליות של גביש מסוג Perovskite, אשר נוצר באמצעות תחמוצת של סטרונציום ונדייט (Strontium Vanadium Oxide – SrVO3).

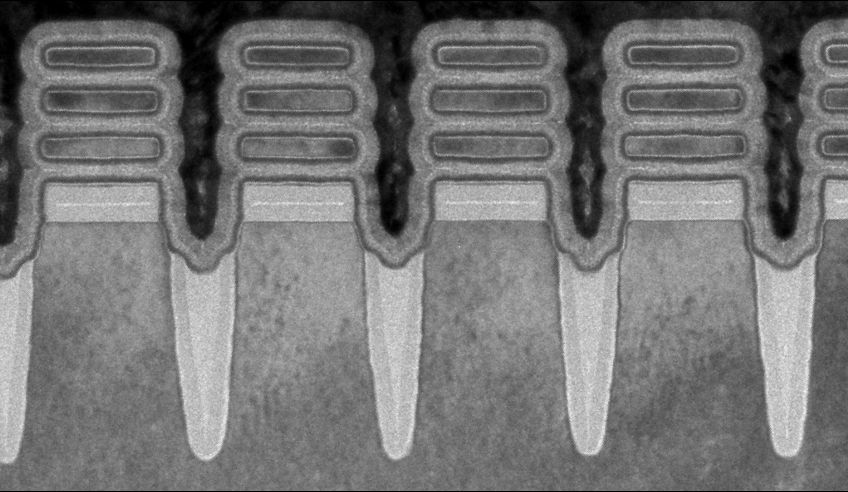

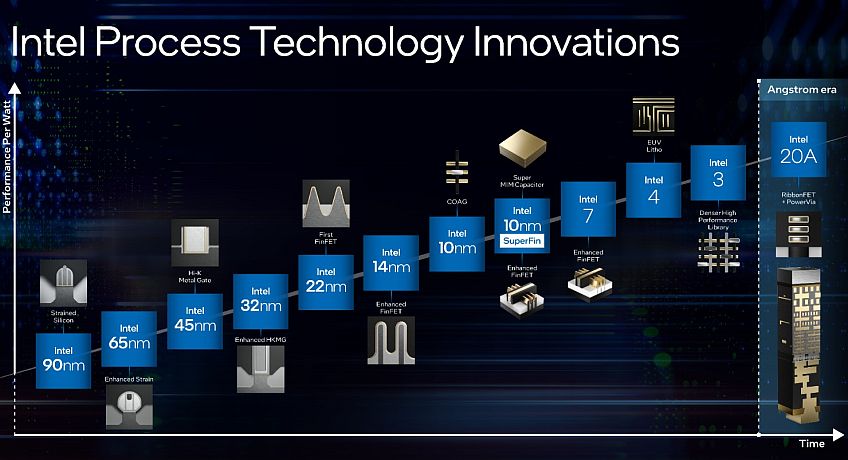

פרופ' קורנבלום, הסביר: "בעקבות המזעור מיוצרים כיום טרנזיסטורים בגודל של כמה עשרות אטומים. במימדים אלו קשה להמשיך במזעור מבלי לפגוע בביצועי הטרנזיסטורים והשבבים המכילים אותם, מכיוון שבסדרי גודל ננומטריים מתנהגים הטרנזיסטורים בדרכים חדשות. למשל נוצרת בעיה קשה של דליפת זרם חשמלי כאשר הטרנזיסטור (המתג) אמור להיות כבוי. דליפה כזו לא רק פוגעת בביצועי הטרנזיסטור, אלא גם מובילה לבזבוז חשמל. בטלפון מודרני המכיל מיליארדי טרנזיסטורים, דליפות זעירות אלה יצטברו לאובדן אנרגיה משמעותי, והתוצאה היא התרוקנות מהירה של הסוללה והתחממות המכשיר. בסדר גודל של חוות שרתים, המשמעות היא צריכת אנרגיה עצומה ושחרור חום רב לאטמוספירה".

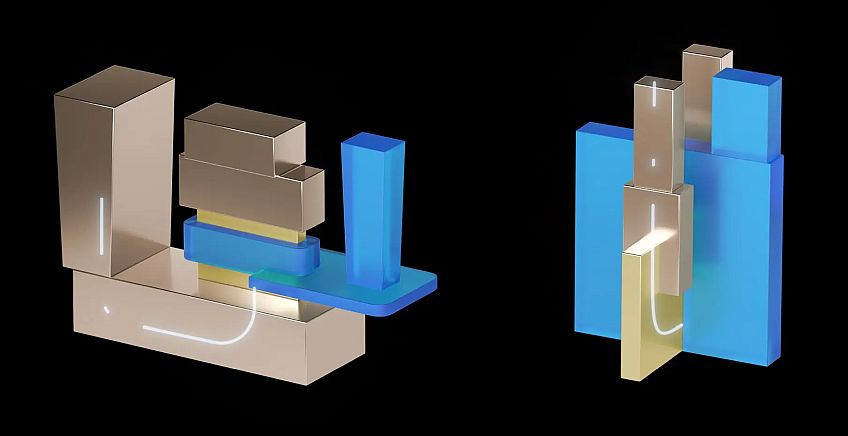

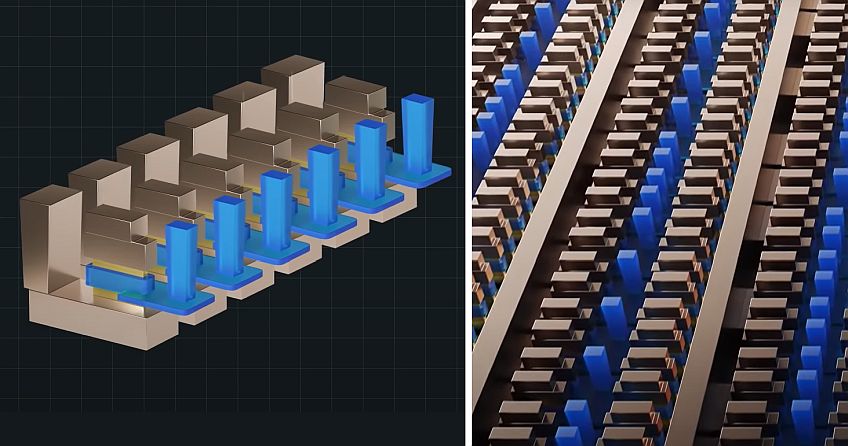

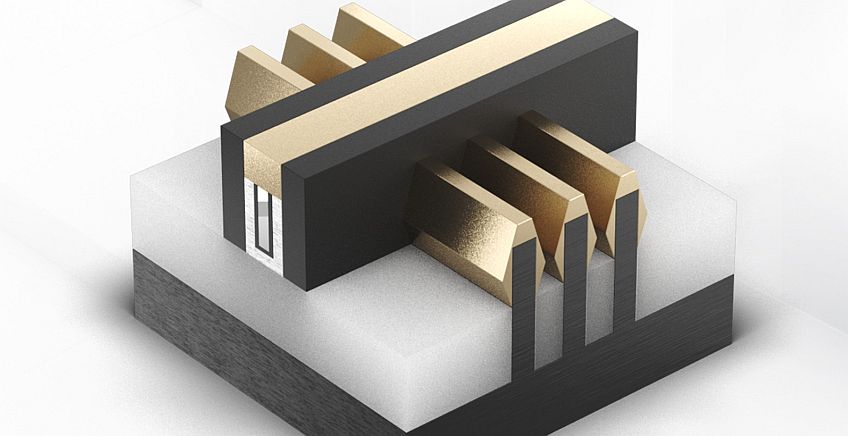

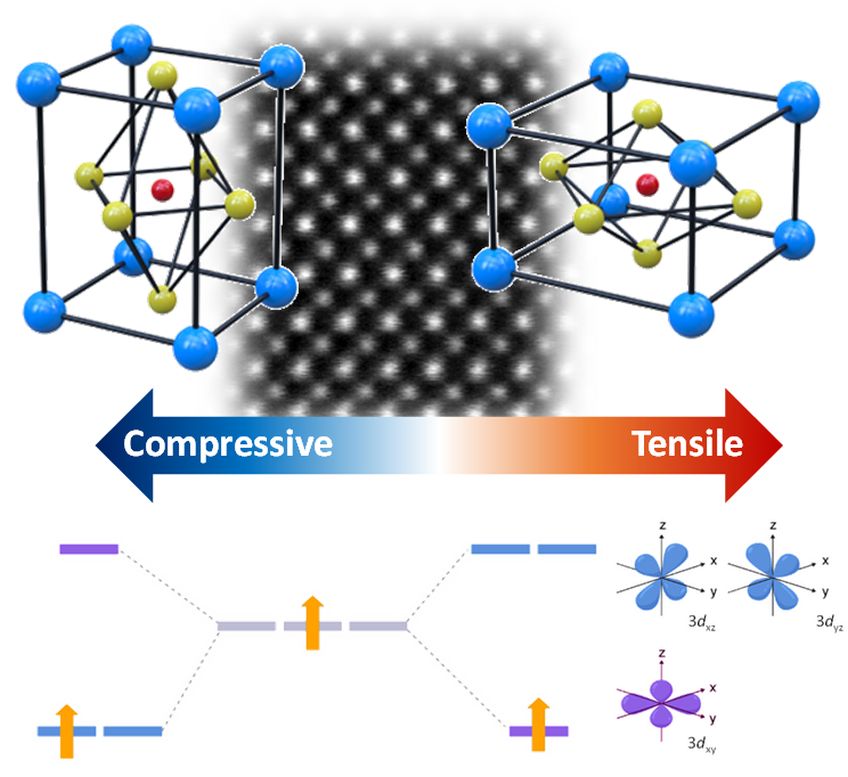

לכן קבוצת המחקר של פרופ' קורנבלום בוחנת תחמוצות שונות אשר יכולות להחליף את הסיליקון, ומתמקדים כעת ב-SrVO3 מכיוון שהיא מסוגלת לשנות את תכונותיה ממוליך חשמלי למבודד, ולהיפך. תכונה שניתן לנצל כדי לייצר מתגים מהירים. הדבר נעשה באמצעות שליטה מדויקת בחומר ובמבנהו האטומי. במאמר שהם פירסמו (הקליקו כאן) הציגו החוקרים שליטה בתכונות החשמליות של החומר באמצעות שליטה מדויקת במרחק שבין האטומים בגביש. מנהלת המעבדה, ד"ר מריה בסקין עושה זאת באמצעות מערכת ייחודית לגידול תחמוצות, באמצעות "הנחת" האטומים במעבדה, שכבה על-גבי שכבה. התהליך מעניק שליטה על המרחקים בין האטומים בכל שכבה ברמת דיוק של פיקומטר (אלפית ננומטר). לצורך השוואה, המרחק בין שני אטומים בסיליקון הוא כרבע ננומטר, שהם 250 פיקומטר.

הדוקטורנטית ליהי שהם חוקרת את תכונות החומר ומייצרת ממנו טרנזיסטור. במחקר הנוכחי היא הובילה צוות של עוד 12 חוקרים מ-8 מוסדות מחקר וחברות בשוויץ, יפן, צרפת וארה"ב. הצוות הראה שעל-ידי מתיחת החומר ברמה האטומית אפשר להאריך את הקשרים הכימיים שלו. כך למשל, מתיחה של פחות מ-2% באורך הקשר הכימי מצמצמת את הנטייה של האלקטרונים לדלג מאטום לאטום. שינויים זעירים אלה מאפשרים לשלוט במעבר בין מצב מוליך למצב מבודד בחומר זה. שהם: "בדקנו את השינויים במאיץ חלקיקים בשווייץ. אלה בדיוק הכלים שאנחנו צריכים לפתח כדי ליצור את הטרנזיסטורים העתידיים. כיום אני מיישמת את תוצאות המחקר על חומרים דומים אחרים, ומהם אני מפתחת טרנזיסטור מסוג חדש".

המחקר נערך במרכז שרה ומשה זיסאפל לננואלקטרוניקה במימון של הקרן הלאומית למדע, והוא נתמך על ידי מכון ראסל ברי לננוטכנולוגיה ותוכנית האנרגיה ע"ש ננסי וסטיבן גרנד.

למאמר ב–Advanced Functional Materials לחצו כאן