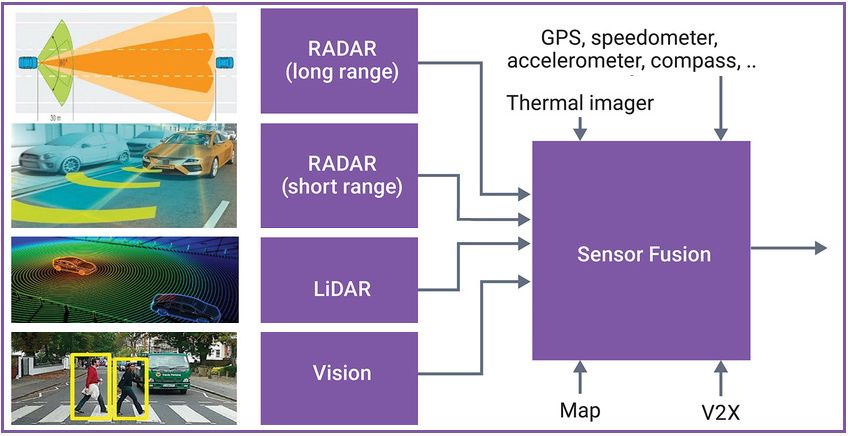

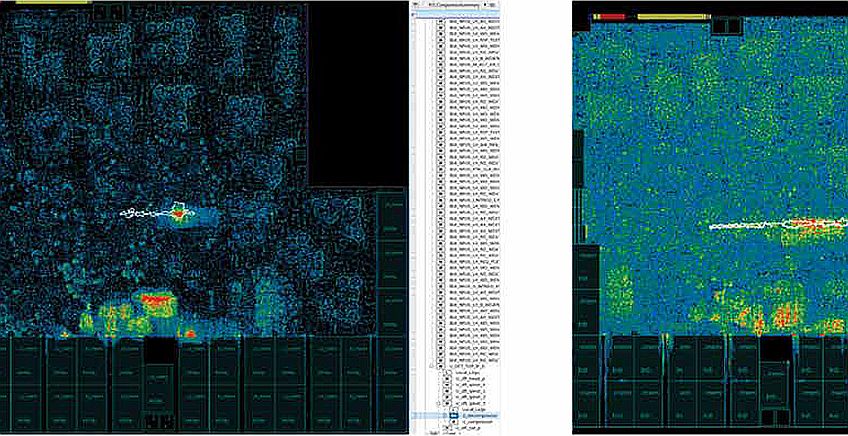

ביום ד’, ה-26 ביולי 2023 בשעה 20:00 לפי שעון ישראל, תקיים חברת סינופסיס (Synopsys) וובינר בנושא מתודולוגיית ביצוע תיקונים של הרגע האחרון בתכנוני מעבדים (RTL engineering change order – ECO), אשר תודגם על-גבי מעבדי RISC-V בעלי עוצמת עיבוד גדולה. מתודולוגיית ECO מאפשרת לבצע תיקונים מקומיים של הרגע האחרון בלא צורך לחזור על כל תהליכי האימות של התכנון השלם. במסגרת ההדגמה יוצגו היכולות של מערכת Formality ECO של חברת סינופסיס.

Synopsys Formality ECO offers an efficient and accurate solution for RTL ECO by automating the comprehensive ECO flow, analysing differences between original RTL and ECO RTL, generating patches, and validating changes. Formality ECO also supports aggressive RTL optimization techniques, including retiming and auto ungrouping, while providing advanced analysis and debug features to streamline the ECO process. In this presentation, we will explore the advantages of Synopsys Formality ECO on the overall ECO cycle including enhanced patching and faster verification runtime leading to improved TAT.

Speakers:

Vivek Upadhyaya (right), Technical Director at SiFive in Physical Implementation Group. His previous roles encompassed notable companies such as Broadcom, Cadence, Intel, and STMicroelectronics, focusing on RTL-to-GDSII implementation. He is graduate from CCS University Meerut, UP.

Vivek Upadhyaya (right), Technical Director at SiFive in Physical Implementation Group. His previous roles encompassed notable companies such as Broadcom, Cadence, Intel, and STMicroelectronics, focusing on RTL-to-GDSII implementation. He is graduate from CCS University Meerut, UP.

Rupali Kale Gaikwad, Staff Engineer at Synopsys. Over a span of 12 years, she has worked on various advanced node ASIC designs of different sectors including automotive, networking, modem, healthcare, high speed CPU implementation. In Synopsys she is responsible for Ecosystem customer success for complete RTL2GDS solution.

למידע נוסף ורישום:

Avinash Palepu, Product Marketing Manager for Formality and Formality ECO products. Starting with Intel as a Design Engineer, he has held various design, AE management and Product Marketing roles in the semiconductor design and EDA industries. Avinash holds a Master’s degree in EE from Arizona State University and a Bachelor’s degree from Osmania University.

Avinash Palepu, Product Marketing Manager for Formality and Formality ECO products. Starting with Intel as a Design Engineer, he has held various design, AE management and Product Marketing roles in the semiconductor design and EDA industries. Avinash holds a Master’s degree in EE from Arizona State University and a Bachelor’s degree from Osmania University. Woo Sung Choe,

Woo Sung Choe,

Jeffrey Lee, Applications Engineer, Senior Staff, Synopsys

Jeffrey Lee, Applications Engineer, Senior Staff, Synopsys Vinkesh Prajapati, Applications Engineer, Senior Manager, Synopsys

Vinkesh Prajapati, Applications Engineer, Senior Manager, Synopsys Jim Schultz, Product Marketing Manager, Synopsys

Jim Schultz, Product Marketing Manager, Synopsys