ביום ה’, ה-22 ביוני 2022, תקיים חברת סינופסיס (Synopsys) וובינר בתחום היישום של שיטות מתקדמות לניתוח ואימות אותות השעון השונים (Clock-Domain Crossing Verification) בתוך ה-SoC, המנהלים את המודולים הנפרדים שמהם השבב בנוי, ולניתוח ואימות ההשבתה של מודולים בלתי פעילים זמנית (Reset Domain Crossing) בתוך השבב. אתגרים אלה נעשים מורכבים מאוד עם המעבר לרכיבים גדולים מאוד הבנויים מתת-מודולים שונים וכוללים אבני בניין (IP Blocks) אשר מגיעים ממקורות שונים. ההדרכה תתקיים בשעה 20:00 לפי שעון ישראל ותימשך 60 דקות.

למידע נוסף ורישום: Constraints-Driven CDC and RDC Verification including UPF Aware Analysis

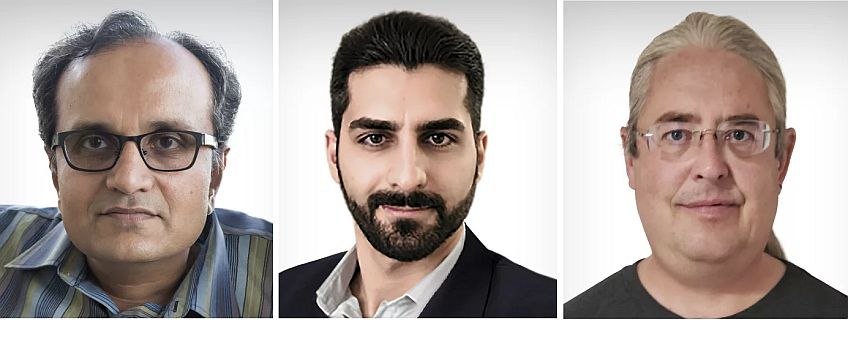

Speakers:

Jerome Avezou (left): Senior Staff Application Engineer in the Customer Success Group at Synopsys. In his current role, he supports static verification products, manages various customer engagements and helps architect customer flows.

Diana Kalel (middle): Hardware verification engineer working on the CDC and RDC analysis at ST Microelectronics. She is currently pursuing a PhD specializing in different structural and functional verification flows of CDC and RDC verification.

Jean-Christophe Brignone (right): Senior Member of Technical Staff (SMTS) in the field of CDC and RDC verification in the CPU division, STMicroelectronics, leading the company-wide reference flow working group.

More about the webinar:

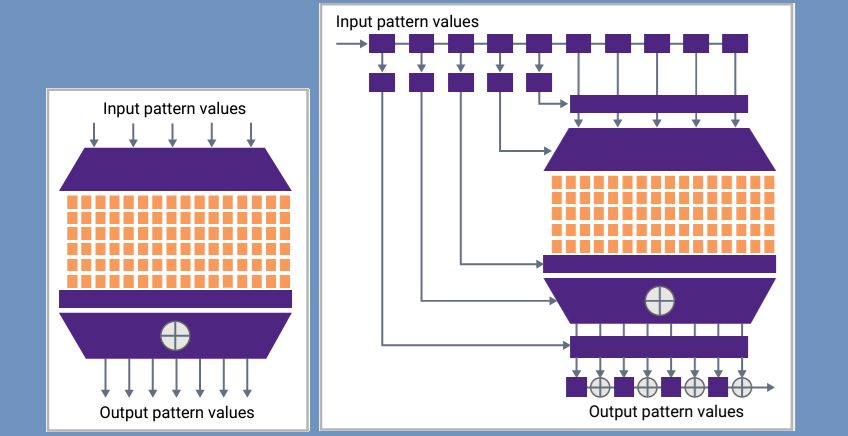

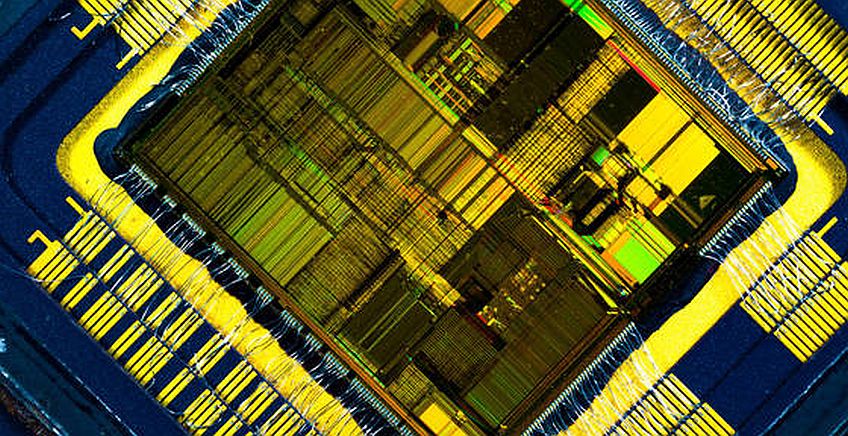

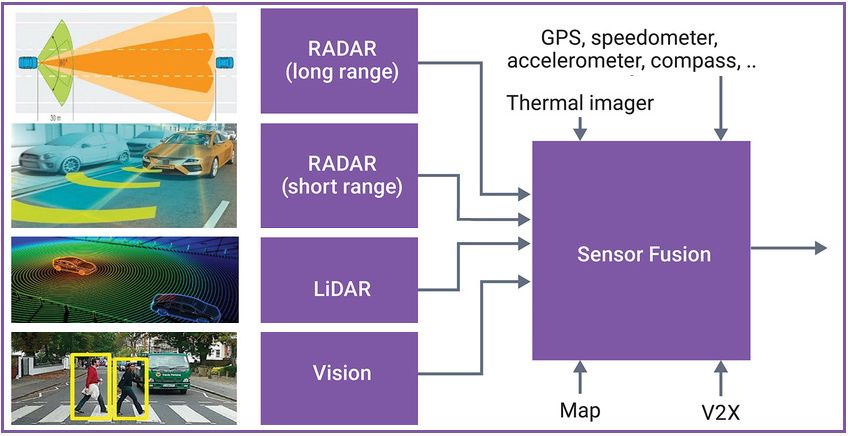

Today’s million gates integrated circuits (ICs) involve various intellectual properties (IPs) interfacing with each other through multiple asynchronous clock and reset domains. Ensuring all clocks propagate concurrently across each clock tree components used as clock switching elements or each sequential or combinatorial component, clock output of which becomes asynchronous with respect to the clock input while maintaining predictability of design functionality requires exhaustive CDC verification.

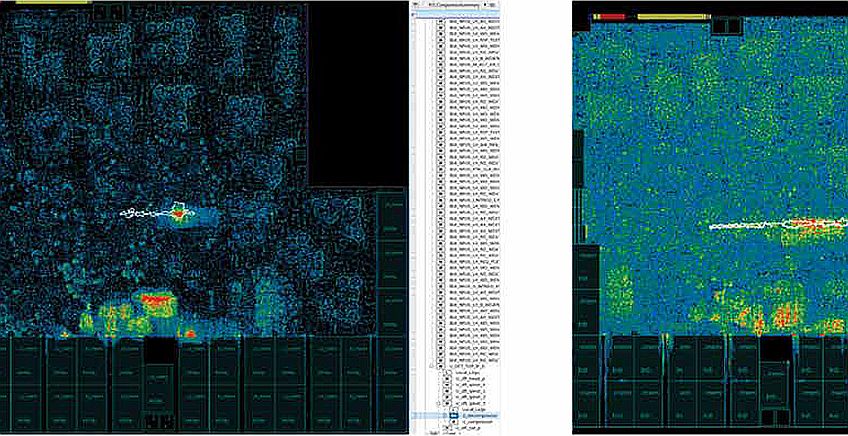

In addition to relying on a robust design specification, it becomes imperative to take advantage of a smart EDA tool that infers all critical design paths including all clocks, clock control signals, clock domain at IP’s boundary level and even the resets for CDC or RDC paths ultimately flagging any unpredictable design behavior. VC SpyGlass CDC and RDC completely meets these verification needs by back-tracing and reporting all signals that needs to be constrained for optimized coverage of the structural verification, eventually delivering high quality of results (QoR) for CDC and RDC analysis.

Proceeding this way prevents the direct reuse of STA (Static Timing Analysis) constraints that may lead to an optimistic configuration, such as the propagation of synchronous clocks instead of asynchronous ones, or other mismatches between CDC analysis and STA, which would limit the number of the analyzed CDC paths.

In this web seminar, we will present the different steps required to manage the constraints generation and elaboration during CDC and RDC analysis. An efficient static low-power verification approach concerning low-power components defined through the UPF file directives will also be illustrated. Lastly, we will conclude by demonstrating ways to manage the different aspects of constraints using VC SpyGlass as an open tcl tool allowing the elaboration of additional and custom features increasing the QoR compared to the native platform.

Part II: Wednesday, November 29, 2023

Part II: Wednesday, November 29, 2023

Vivek Upadhyaya (right), Technical Director at SiFive in Physical Implementation Group. His previous roles encompassed notable companies such as Broadcom, Cadence, Intel, and STMicroelectronics, focusing on RTL-to-GDSII implementation. He is graduate from CCS University Meerut, UP.

Vivek Upadhyaya (right), Technical Director at SiFive in Physical Implementation Group. His previous roles encompassed notable companies such as Broadcom, Cadence, Intel, and STMicroelectronics, focusing on RTL-to-GDSII implementation. He is graduate from CCS University Meerut, UP.

Avinash Palepu, Product Marketing Manager for Formality and Formality ECO products. Starting with Intel as a Design Engineer, he has held various design, AE management and Product Marketing roles in the semiconductor design and EDA industries. Avinash holds a Master’s degree in EE from Arizona State University and a Bachelor’s degree from Osmania University.

Avinash Palepu, Product Marketing Manager for Formality and Formality ECO products. Starting with Intel as a Design Engineer, he has held various design, AE management and Product Marketing roles in the semiconductor design and EDA industries. Avinash holds a Master’s degree in EE from Arizona State University and a Bachelor’s degree from Osmania University. Woo Sung Choe,

Woo Sung Choe,

Jeffrey Lee, Applications Engineer, Senior Staff, Synopsys

Jeffrey Lee, Applications Engineer, Senior Staff, Synopsys Vinkesh Prajapati, Applications Engineer, Senior Manager, Synopsys

Vinkesh Prajapati, Applications Engineer, Senior Manager, Synopsys Jim Schultz, Product Marketing Manager, Synopsys

Jim Schultz, Product Marketing Manager, Synopsys