חברת Satixfy מרחובות דיווחה על הכנסות של 6.1 מיליון דולר במחצית הראשונה של 2024 – עלייה של 7% בהשוואה לתקופה המקבילה ב-2023. שולי הרווח השתפרו משמעותית מ-47% בשנה שעברה ל-71% במחצית הראשונה של 2024, ובעקבות כך גם ההפסד הנקי הצטמצם והסתכם ב-21.3 מיליון דולר – לעומת הפסד נקי של 46.3 מיליון דולר במחצית הראשונה של 2023.

בקופת המזומנים של החברה היו, נכון לסוף חודש יוני, 7.4 מיליון דולר. בסטיקספיי ציינו כי מירב ההכנסות הגיעו ממכירת דוגמאות של שבבי ASIC ייעודיים ללוויינים בחלל. זהו קו מוצרים שבחברה מקווים שיוביל להתאוששות בפעילותה המסחרית.

בשנת 2022 נקלעה סטיקספיי למשבר עסקי והכנסותיה השנתיות ירדו בכ-50% ל-10.6 מיליון דולר. ב-2023 חל שיפור מזערי לרמה של 10.7 מיליון דולר. מניית סטיקספיי נסחרת בנסד"ק לפי שווי של 58 מיליון דולר בלבד, לאחר שאיבדה יותר מ-92% מערכה מאז הנפקתה. עם זאת, מאז תחילת השנה ניכרת התאוששות מסוימת והמניה עלתה ב-92% ממחיר השפל.

בחודש יוני דיווחה סטיקספיי על חוזה עם חברה, שנותרה חסויה, לאספקה של שבבי Prime2 בהיקף של 20 מיליון דולר. ההזמנה תסופק על פני חמישה רבעונים, והמערכות ישמשו את הלקוח כחלק מפריסת קונסטלציית לוויינים במסלול-נמוך (LEO). זוהי הזמנה שנייה מצד אותו לקוח, המצטרפת להזמנה בהיקף של 4 מיליון דולר בספטמבר 2023.

PRIME2 הוא שבב בקרת עיצוב האלומה (beamformer) המנהל מערכים מרובי אנטנות (MIMO) בלוויינים נמוכי מסלול ובפלטפורמות מוטסות המתקשרות גם אל לוויינים גבוהי מסלול (GEO). שבב נוסף בקו המוצרים החללי הוא ה-Sx4000, שהוא רדיו מוגדר תוכנה (SDR) המותקן בלוויין מסלול נמוך (LEO). השבבים הללו צפויים להיכנס לייצור סדרתי באמצע 2025.

ניר ברקן, מנכ"ל סטיקספיי, אמר: "אנחנו מאוד מרוצים מההתקדמות שעשינו ב-2024, שבא לידי ביטוי בגידול סולידי בהכנסות וברווחיות, בעיקר בזכות מכירת דוגמאות הנדסיות של שבבי ה-ASIC החלליים שלנו".

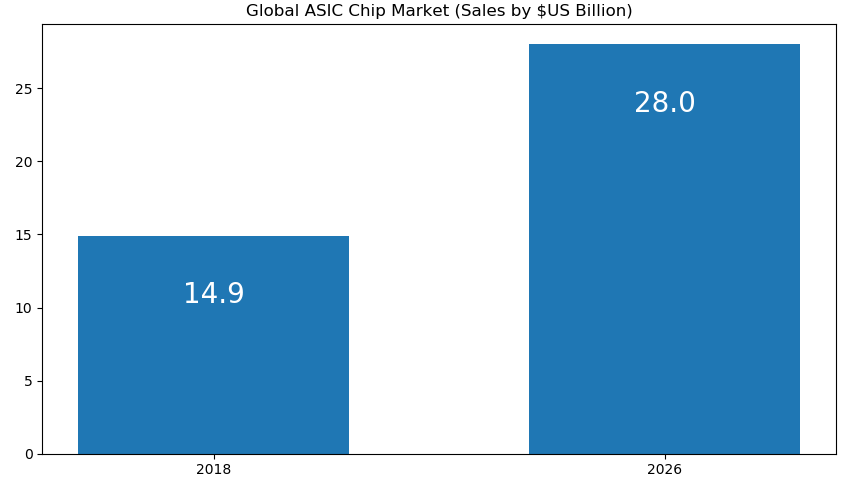

בחלוקה לפי יישומים, מערכות עיבוד נתונים תפסו כרבע משוק ה-ASIC העולמי בשנת 2018, בזכות האימוץ הגובר של רכיבי ASIC לביצוע יישומים במרכזי נתונים , במערכות ובמתגי תקשורת, בתחנות בסיס סלולריות ובמערכות אלחוטיות מסוגים שונים. אולם במבט לעתיד, שוק מוצרי הצריכה צפוי להיות השוק בעל הצמיחה המהירה ביותר, של 13.2% בשנה. זאת בעקבות החדירה הגוברת של רכיבי ASIC למוצרי צריכה כמו טלוויזיות, מצלמות דיגיטליות, קונסולות משחקים ואפילו מכשירי סמארטפון.

בחלוקה לפי יישומים, מערכות עיבוד נתונים תפסו כרבע משוק ה-ASIC העולמי בשנת 2018, בזכות האימוץ הגובר של רכיבי ASIC לביצוע יישומים במרכזי נתונים , במערכות ובמתגי תקשורת, בתחנות בסיס סלולריות ובמערכות אלחוטיות מסוגים שונים. אולם במבט לעתיד, שוק מוצרי הצריכה צפוי להיות השוק בעל הצמיחה המהירה ביותר, של 13.2% בשנה. זאת בעקבות החדירה הגוברת של רכיבי ASIC למוצרי צריכה כמו טלוויזיות, מצלמות דיגיטליות, קונסולות משחקים ואפילו מכשירי סמארטפון.