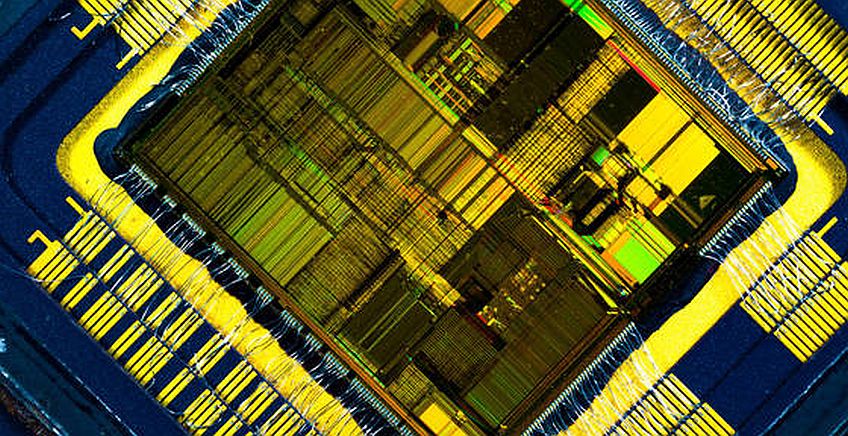

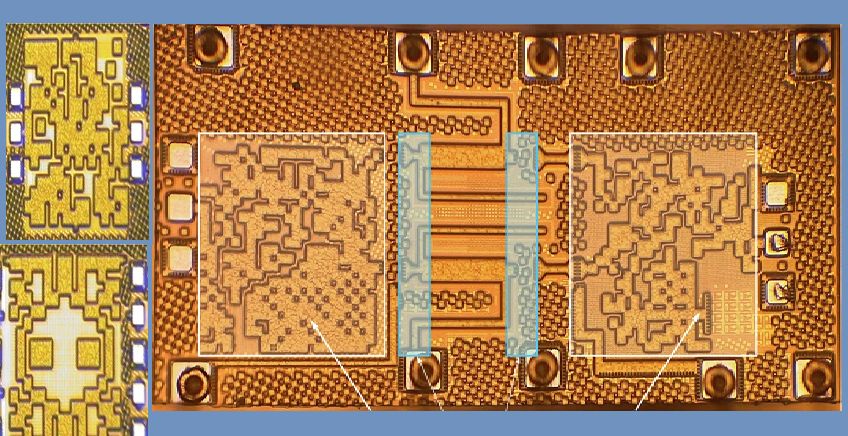

בתמונה: תרשים תכנון שבב התקשורת. מתוך המחקר שפורסם ב-Nature Communications

מאת יוחאי שויגר

חוקרים מהפקולטה להנדסה באוניברסיטת פרינסטון ובאוניברסיטה הטכנולוגית של הודו (IIT), שפיתחו מודל בינה מלאכותית כדי לתכנן שבבי תקשורת אלחוטיים, נתקלו בתופעה מפתיעה. במחקר שפורסם בעיתון המדעי Nature Communications דיווחו החוקרים על הניסוי, והראו שלא זו בלבד שהמודל סייע לקצר משמעותית את זמני התכנון של מעגלים מורכבים ועתירי ביצועים משבועות לדקות – הוא גם הפיק תכנונים בלתי צפויים שלהערכת החוקרים היו מקוריים וחדשניים מאוד, באופן החורג מיכולת ההבנה של מהנדס בשר-ודם.

החוקרים התמקדו בתכנון מעגלי תקשורת בגלים מילימטריים בתדרים הקרובים לתדרי טרה-הרץ (Thz). תקשורת בתדרים האלה מיועדת לספק רוחב פס גדול וקישוריות מהירה ואמינה, וצפויה לספק את התשתית העתידית לתקשורת האלחוטית של הדור השישי (6G) ולפתרונות חישה ברזולוציה גבוהה. אולם התכנון של מעגלים כאלה הוא קשה ומצריך מיומנות גדולה ונסיון רב. בשיטות הקיימות היום, המהנדס מתחיל את מלאכת התכנון "מלמטה למעלה", עם מבנה אלקטרומגנטי וטופולוגיה מוגדרים מראש, ואז מתקדם צעד אחר צעד, בתהליך של אופטימיזציה, עד להשגת תוצאה משביעת רצון.

השיטה הזו כוללת מידה רבה של ניסוי וטעיה והפקת גרסאות רבות של התכנון, עד להשגת התכנון הסופי. המודל הנוירוני שפיתחו החוקרים פועל הפוך: "מלמעלה-למטה" (inverse design). המודל מייצר מבנה אלקטרומגנטי ואת המעגל התואם לו בהתאם לפרמטרים התכנוניים הכלליים, כמו למשל התדר והספק המעגל המתוכנן. החוקרים דיווחו שהמודל הפיק בתוך דקות ספורות תכנוני מעגלים מורכבים, שהציגו ביצועים גבוהים מאוד, ברמה שאינה אפשרית בשיטות התכנון הקיימות.

לאלגוריתם יש גישה תכנונית לא-אנושית

אלא שקיצור תהליכים ושיפור בביצועים לא היו גולת הכותרת של המחקר: מאחר שלא הוגבל מראש למבנים ולטופולוגיות סדורים מספרי הלימוד, המודל ייצר תכנונים "מוזרים" וחדשים לגמרי. החוקר הראשי שהוביל את הניסוי, פרופ' קשיק סנגופטה (Kaushik Sengupta), אמר למגזין של אוניברסיטת פרינסטון כי התכנונים היו "לא-אינטואיטיביים וכאלה שלא סביר שמהנדס אנושי יתכנן. קיבלנו מבנים מורכבים ובעלי צורה הנראית אקראית. כאשר בנינו את המעגלים שהמודל תכנן, קיבלנו ביצועים שעד כה היו בלתי מושגים. בני אדם לא מסוגלים להבין את המעגלים הללו, אך הם עובדים טוב יותר ממעגלים שתוכננו על-ידי מהנדסים".

חוקר נוסף שהוביל את המחקר, עודאי קנקייג'ו (Uday Khankhoje), הסביר כי הגישה החדשה תסייע להתמודד עם אתגרים בתחום הנדסת האלקטרוניקה, שכיום אינם פתירים. "המחקר הזה מספק הצצה לעתיד מבטיח. הבינה המלאכותית לא רק מאיצה סימולציות אלקטרומגנטיות שגוזלות זמן רב, אלא מאפשרת לחקור עולם חדש של תכנוני שבבים שעד כה היה בלתי נודע, ולייצר מכשירים עתירי ביצועים שחורגים מכללי ההיגיון האנושיים. זהו רק קצה הקרחון".

המהנדסים לא מבינים

הקונפיגורציות האפשריות בתכנון מעגלים מעין אלה הן כמעט אינסופיות, ומהנדס אנושי יכול לבחון רק מספר מוגבל של אפשרויות, ובתוך מסגרת נתונה של מבנים וטופולוגיות. לדברי החוקרים, המודל שלהם יצר תכנוני מעגלים בדפוסים "אקראיים" לכאורה ובלתי צפויים, שקשה לפצח את ההיגיון שעמד מאחוריהם. "מהנדסים אנושיים לא יכולים להבין רמה כזו של מורכבות, ועל כן הם בונים מעגלים משולבים 'מלמטה-למעלה', מוסיפים רכיב לפי הצורך ומתאימים את התכנון תוך כדי תהליך הבנייה. ה-AI, לעומת זאת, רואה את השבב כמבנה יחיד. הדבר מוביל לתצורות מוזרות אך יעילות".

Part I: Wednesday, November 8, 2023

Part I: Wednesday, November 8, 2023