ביום ד', ה-6 במאי 2026, תקיים חברת סינופסיס (Synopsys) וובינר שיוקדש לבדיקות זמנים והספק אחרונות של השבב לפני היציאה לייצור (Signoff). ההדרכה תתמקד בהבנת בדיקות EMIR Signoff הכוללות Electromigration (EM) ובדיקות נפילת מתח ברשת ההזנה (IR Drop), אשר פוגעות בביצועי השבב ובהופעת בעיות תיפקוד לאחר הייצור.

בהמשך, הדרכה תתאר את המעבר אל הגישה המודרנית של נתיוח דינמי תחת הדמיית עומס, איתור בעיות, טיפול בבעיות והרצה נוספת, עד לקלבת הפתרון המספק (IR-Aware Design Closure). ההדרכה המקוונת תשודר בשעה 20:00 לפי שעון ישראל ותימשך 60 דקות. היא תתקיים תחת הכותרת: RedHawk-SC: From EMIR Signoff to IR-Aware Design Closure.

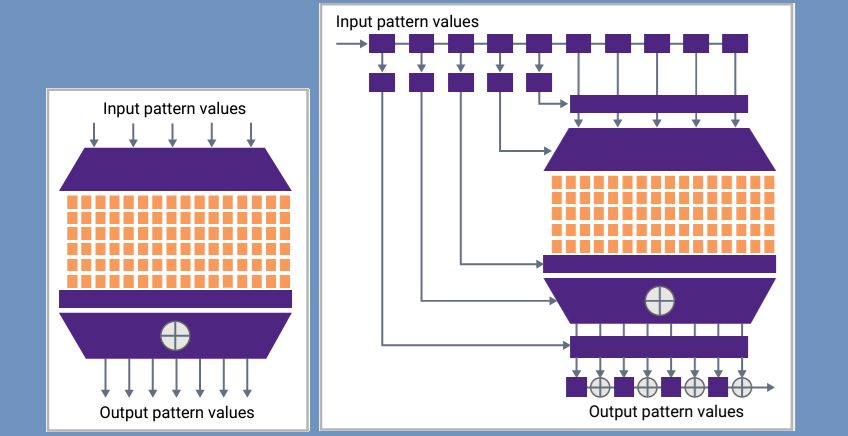

As power integrity challenges increase with advanced nodes and multi-die architectures, EMIR analysis must evolve beyond traditional signoff. In this Synopsys webinar, we will show how RedHawk-SC is expanding its capabilities not only to enhance EMIR analysis, but also to enable IR-aware Static Timing Analysis (IR-STA) and IR-driven ECO (IR-ECO) flows.

As power integrity challenges increase with advanced nodes and multi-die architectures, EMIR analysis must evolve beyond traditional signoff. In this Synopsys webinar, we will show how RedHawk-SC is expanding its capabilities not only to enhance EMIR analysis, but also to enable IR-aware Static Timing Analysis (IR-STA) and IR-driven ECO (IR-ECO) flows.

Join us to learn how tighter integration between power integrity and timing analysis, across both single-die and multi-die designs, helps engineers better understand IR-drop impact, accelerate debug, and achieve faster, more reliable design closure.

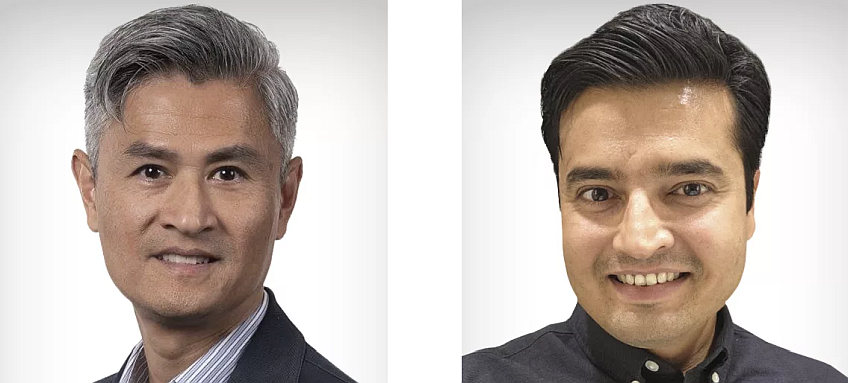

Featured Speaker: Sojan Philips is the Principal Product Manager for RedHawk-SC at Synopsys with over 10 years of experience in the semiconductor and EDA industry. He specializes in driving product innovation at the intersection of engineering and customer needs, with a strong focus on power integrity and large-scale design analysis.

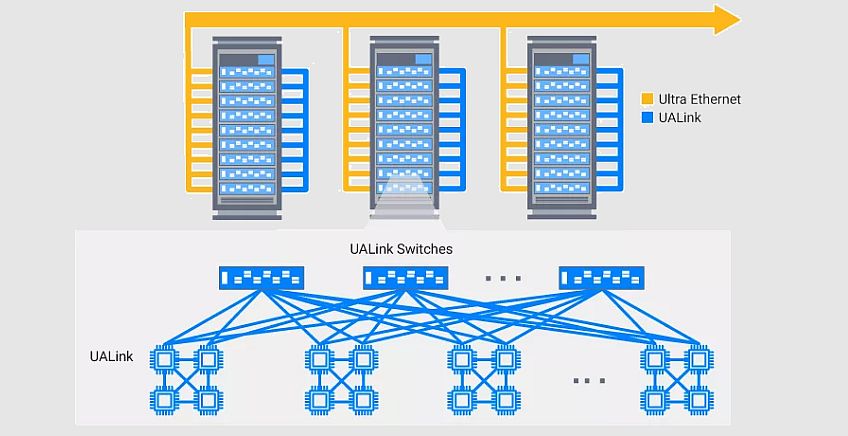

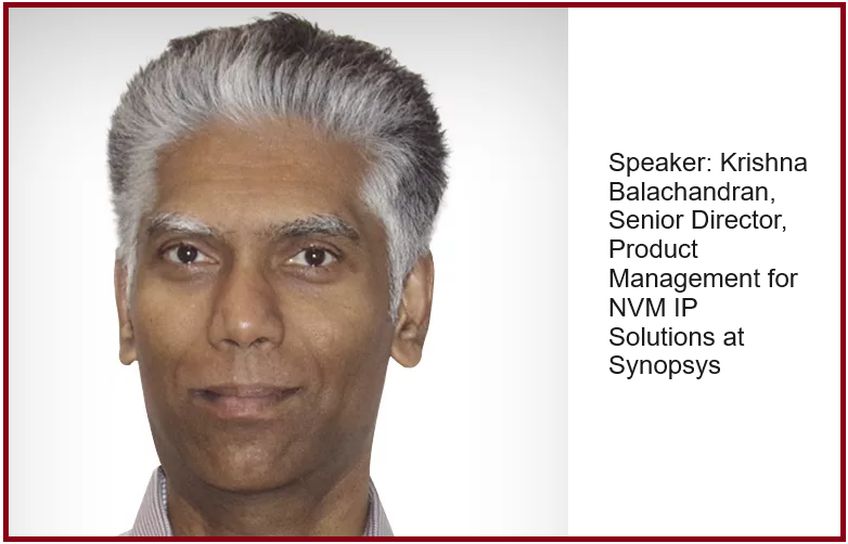

Speaker: Diwakar Kumaraswamy, Technical Product Manager at Synopsys with over 15 years of experience in SoC design and high-speed interconnects. He specializes in PCIe architecture for AI and HPC, supporting next-generation connectivity solutions for advanced infrastructure.

Speaker: Diwakar Kumaraswamy, Technical Product Manager at Synopsys with over 15 years of experience in SoC design and high-speed interconnects. He specializes in PCIe architecture for AI and HPC, supporting next-generation connectivity solutions for advanced infrastructure.

Key benefits of migrating to PCIe 5.0

Key benefits of migrating to PCIe 5.0

Speaker: Jim Schultz, senior staff product manager for the Synopsys EDA Group. He holds a B.S. in electrical engineering from the University of California, Davis with an emphasis in electromagnetics. His design engineering experience includes physical verification, design planning and design implementation on CPUs, networking and security chips. As a product engineer, he has supported design implementation, design planning and package design at various EDA companies.

Speaker: Jim Schultz, senior staff product manager for the Synopsys EDA Group. He holds a B.S. in electrical engineering from the University of California, Davis with an emphasis in electromagnetics. His design engineering experience includes physical verification, design planning and design implementation on CPUs, networking and security chips. As a product engineer, he has supported design implementation, design planning and package design at various EDA companies.

Part II: Wednesday, November 29, 2023

Part II: Wednesday, November 29, 2023