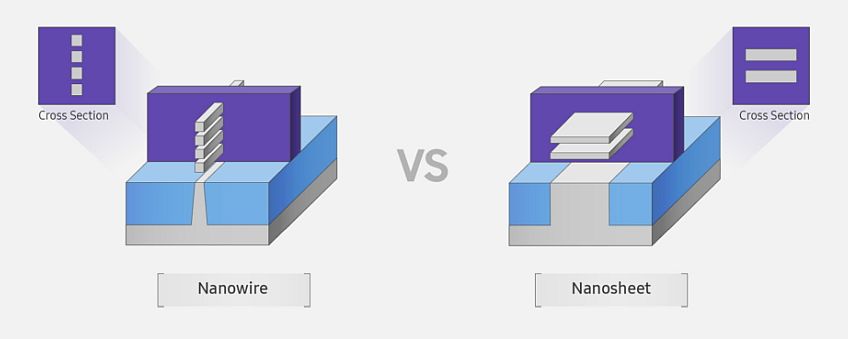

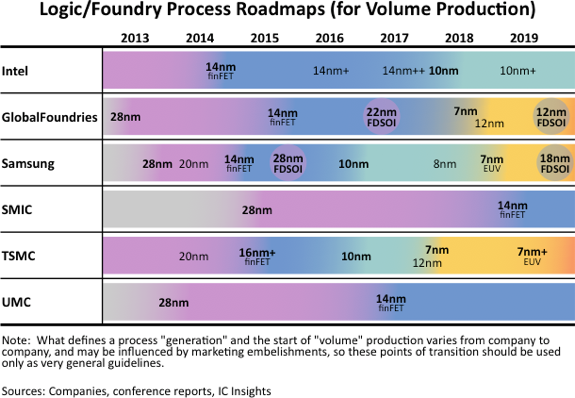

למרות שהייתה מחלוצות המעבר אל טרנזיסטורי Gate-All-Around (GAA), חברת סמסונג פתחה בקמפיין שיווק של טכנולוגיית הייצור הקודמת המבוססת על טרנזיסטורי FInFET ברוחב צומת של 4 ננומטר. לפני שבוע החברה הכריזה על דור חדש של תהליך 4nm FinFET, שהוא למעשה אופטימיזציה של תהליך ותיק מאוד – וזה בעצם הייחוד שלו. החברה הוסיפה מספר יכולות בחירה בפרמטרים שונים כגון מהירות התגובה ומתחי השער, ועל-ידי כך, לטענתה, היא מספקת את הצרכים של שווקים מגוונים, החל ממרכזי AI וכלי רכב, וכלה במוצרים חסכוניים מאוד באנרגיה. היתרון הגדול של טכנולוגיית היצור הזו לא טמון במיזעור או מהירות יוצאת דופן – אלא בכך שהתהליך עבר דורות רבים של תיקון תקלות ו"שיוף" קצוות, שהפך אותו לאמין וזול מאוד שהשוואה לבילת הביצועים שהוא מספק.

בכך היא מנסה למעשה לחזור על ההצלחה של תהליך 28 ננומטר, אשר נחשב עד לפני כ-10 שנים לתהליך הייצור הכדאי ביותר שסיפק לחברות את נקודת האיזון הטובה ביותר בין ביצועים, מחיר ואמינות (yield). בבלוג הטכנולוגי שלה, החברה הסבירה שתהליך 4nm FinFET "ממוקם בנקודת המפגש שבין טכנולוגיות ייצור מתקדמות לבין טכנולוגיות בוגרות. הוא מאזן בין ביצועים לבין יכולת ייצור סדרתי יעילה". כדי למקם אותו בנקודה הזו, ביצעה סמסונג מספר שיפורים ייעודיים בתהליך:

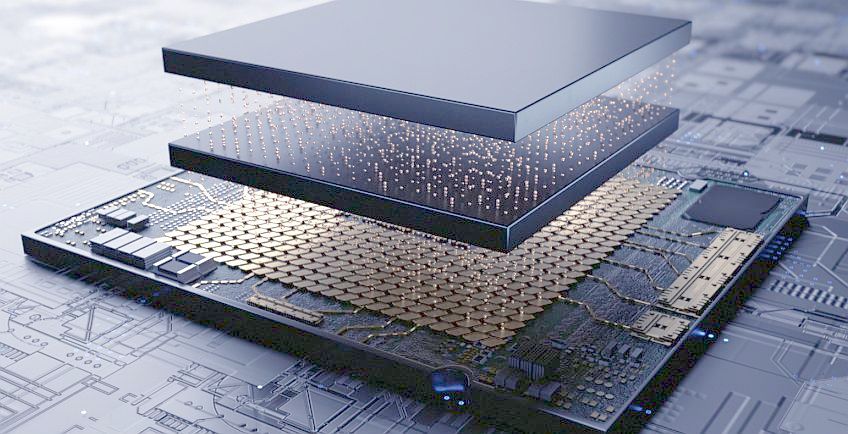

היא מאפשרת להגדיר את מתחי הסף (Threshold Voltage – Vth) של הטרנזיסטורים בשב. כך למשל, רכיבי uLVT (Ultra-Low Vth) משפרים את מהירות המיתוג ומתאימים במיוחד לתכנונים עתירי ביצועים, אולם בעלי צריכת אנרגיה גבוהה יחסית. לעומתם רכיבי HVT (High Vth) איטיים יותר אולם מפחיתים את זרם הדליפה ובכך מקטינים את צריכת ההספק של השבב. החברה ביצעה שינויים במערך שכבות הקישוריות (interconnect stack) כדי לעניק שליטה רחבה יותר במאפייני ההתנגדות־קיבוליות (RC) של המוליכים החשמליים. במעגלים ממוזערים, העלייה בהתנגדות ובקיבוליות של שכבות המתכת מגבילה את מהירות התקדמות האותות. סמסונג הוסיפה שכבות קישוריות נוספות בעלות Pitch גדול יותר ומאפייני התנגדות־קיבוליות (RC) משופרים, שהובילו להפחתה של כ־26% בהשהיית RC.

אופטימיזציה של צריכת הספק ויעילות תרמית

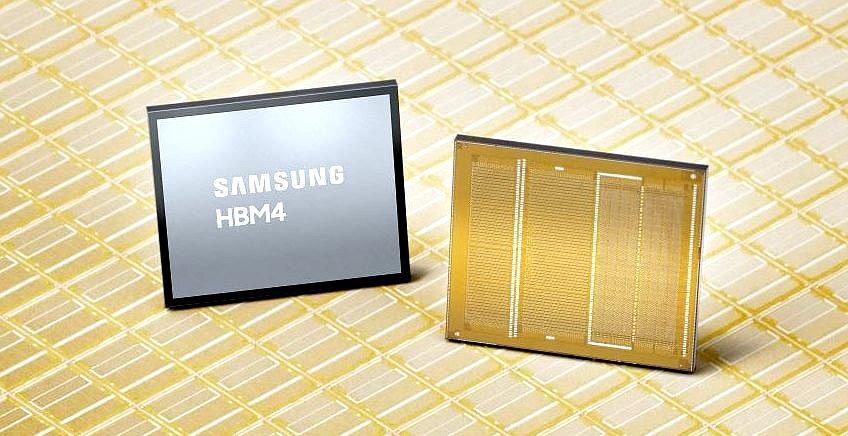

אחד מהיתרונות שהחברה מקדמת הוא שמדובר בתהליך גמיש המתאים ליישומים שונים, גם אנלוגיים וגם דיגיטליים. כך למשל, זיכרונות HBM4 דורשים רוחב פס גבוה לצורך העברת נתונים בהיקפים גדולים, תוך פעולה במרחב פיזי מוגבל שבו צפיפות ההספק והניהול התרמי הם גורמים קריטיים. בסביבה כזו, יעילות ואיזון תרמי חשובים לעיתים יותר מאשר ביצועי שיא. תהליך ה־4 ננומטר ממזער הפסדי הספק באמצעות פעולה במתח נמוך ושכבות קישוריות בעלות התנגדות נמוכה, ובכך מאפשר תכנונים יעילים במיוחד גם בתרחישים של אינטגרציה צפופה. מאפיינים אלו הופכים אותו למתאים במיוחד למימוש שכבת ה־Base Die בזיכרונות HBM.

יישומי AI ו־HPC דורשים ארכיטקטורות שבבים גדולות (Large Die), אולם ככל ששטח השבב גדל, כך עולה גם ההסתברות לפגמים. בהקשר זה, החברה מאמינה, התהליך מספק את רמת האמינות הנדרשת. "יחידת LPU (Language Processing Unit) של חברה אמריקאית מובילה, משתמשת בתהליך ה־4 ננומטר כדי להשיג גם קישוריות בצפיפות גבוהה ויעילות הספק, כאשר הדור הבא של יחידות ה-LPU ייכנס לייצור המוני במחצית השנייה של 2026".

"רכיבי SerDes הפועלים במהירויות של עשרות גיגה־ביט לשנייה, רגישים מאוד לשונות בתהליך הייצור ודורשים איזון מדויק בין שלמות אות (Signal Integrity – SI) לבין יעילות הספק. בנוסף, התמיכה ב־IP בדרגת תקן רכב דוגמת LPDDR, PCIe, MIPI M-PHY, HDMI ו־USB מתאימה ליציור של מערכות ADAS ו-IVI, ותומכת במגוון רחב של פונקציות ברכב, החל מעיבוד חיישנים ועד להעברת נתונים במהירות גבוהה". החברה גם מדגישה בקמפיין ששוק ה־RF נמצא בתהליך מעבר מארכיטקטורות RFIC מסורתיות לתכנוני RF SoC בעלי אינטגרציה דיגיטלית רבה. "תהליך ה־4 ננומטר מתאים במיוחד לתכנוני RF SoC משולבי אותות (Mixed-Signal) לסביבות תקשורת מהדור הבא, כגון Wi-Fi 8 ו־6G".