בתמונה למעלה: ד"ר ליסה סו, מנכ"לית, נשיאה, ומעכשיו גם יו"ר חברת AMD

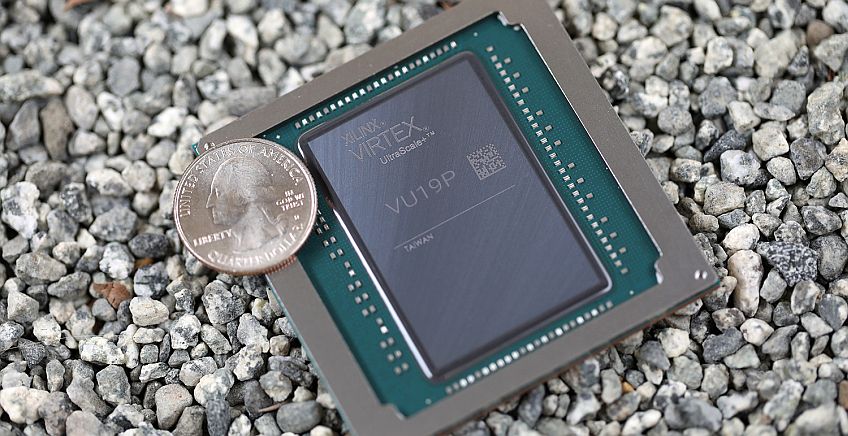

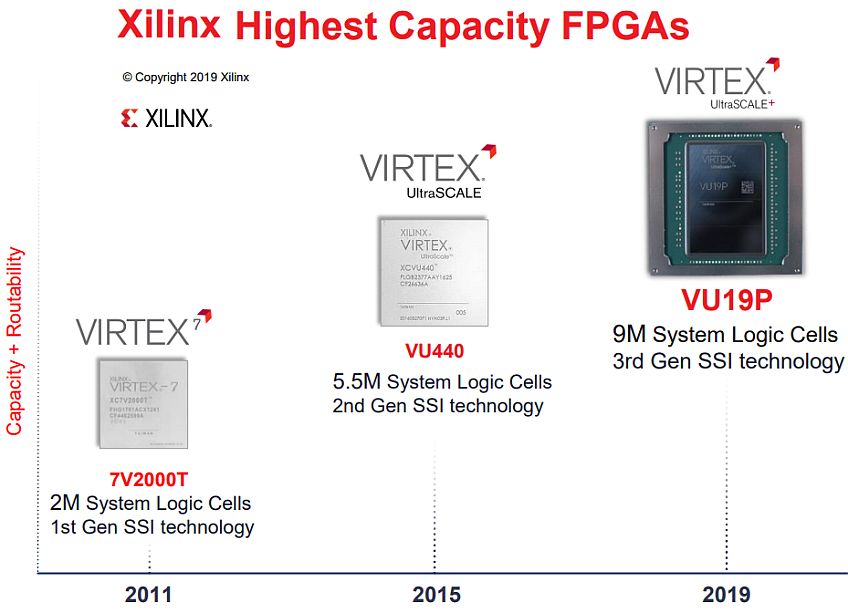

חברת AMD הודיעה היום (ב') על השלמת עסקת הרכישה של חברת Xilinx. מדובר באחת מעסקות המיזוג הגדולות ביותר בתעשיית השבבים, אשר הוכרזה באוקטובר 2020, והמתינה עד היום לקבלת כל האישורים הרגולטוריים. במקור, מדובר היה בעסקת מניות בשווי של כ-35 מיליארד דולר, אולם בעקבות העליות במניית AMD בשנה האחרונה, מגיע היקף העיסקה לכ-50 מיליארד דולר – סכום שעושה אותה לעסקת השבבים הגדולה ביותר בעולם.

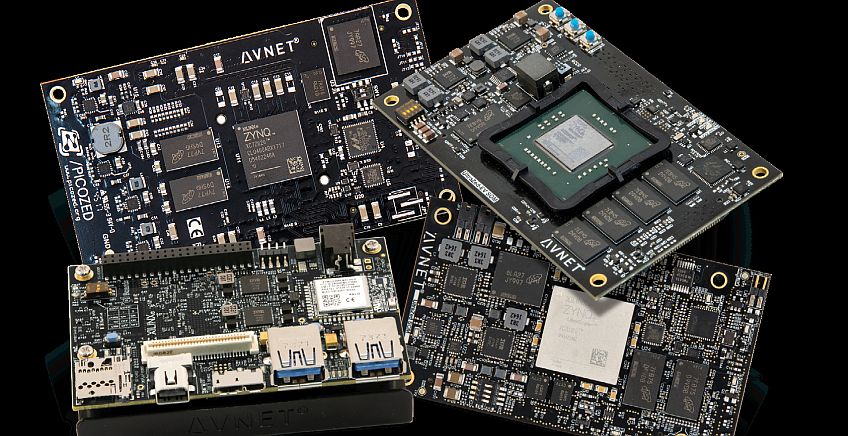

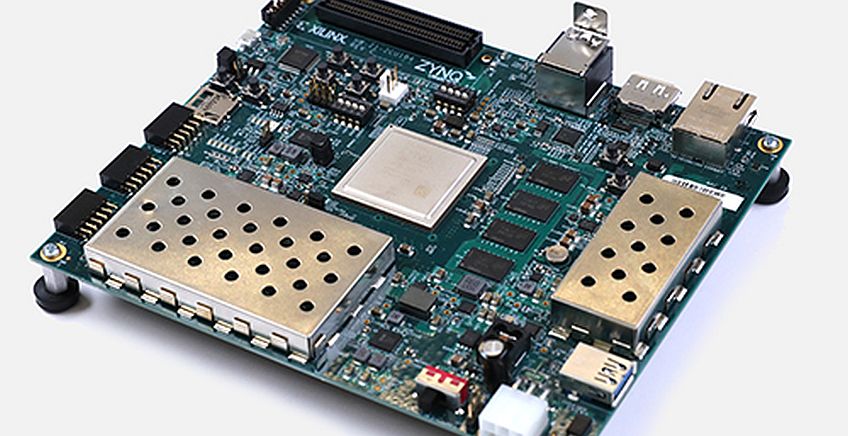

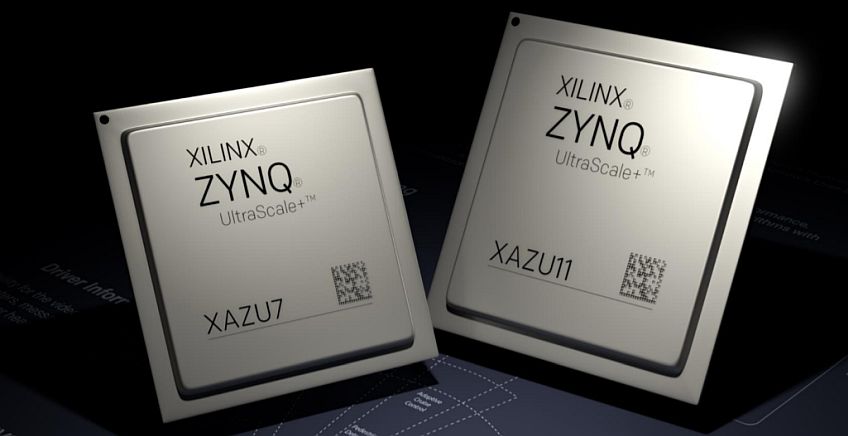

חברת AMD קיבלה לידיה את כל העובדים והנכסים של חברת Xilinx. בעלי המניות של זיילינקס מקבלים 1.72 מניות AMD עבור כל מניה של Xilinx. חברת זיילינקס הפסיקה להיסחר בבורסה והפכה לחטיבת ה-FPGA והמחשוב המסתגל של AMD. החטיבה החדשה תיקרא Adaptive and Embedded Computing Group – AECG, ותנוהל על-ידי ויקטור פנג, אשר שימש כמנכ"ל זיילינקס. בין השאר, תפקידו יהיה להגדיר מפת דרכים עבור מוצרים חדשים אשר משלבים בין הפתרונות של זיילינקס ובין מעבדי ה-CPU וה-GPU של AMD. תקציב המו"פ המשותף של שתי החברות יסתכם בכ-3.8 מיליארד דולר.

שוק יעד בהיקף של 135 מיליארד דולר

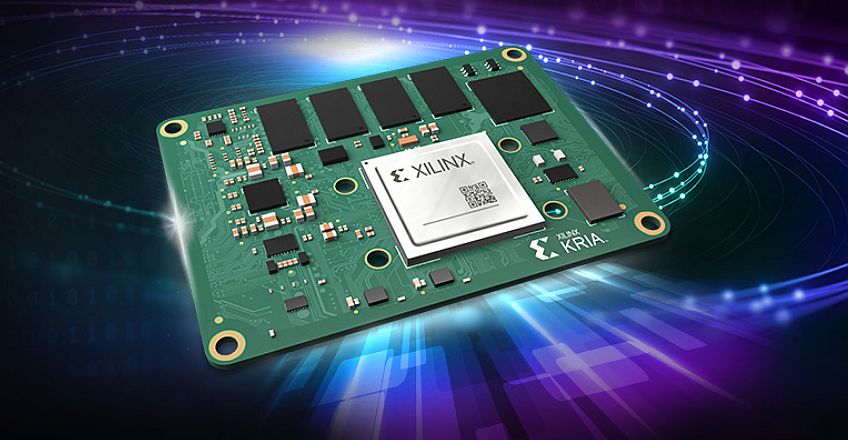

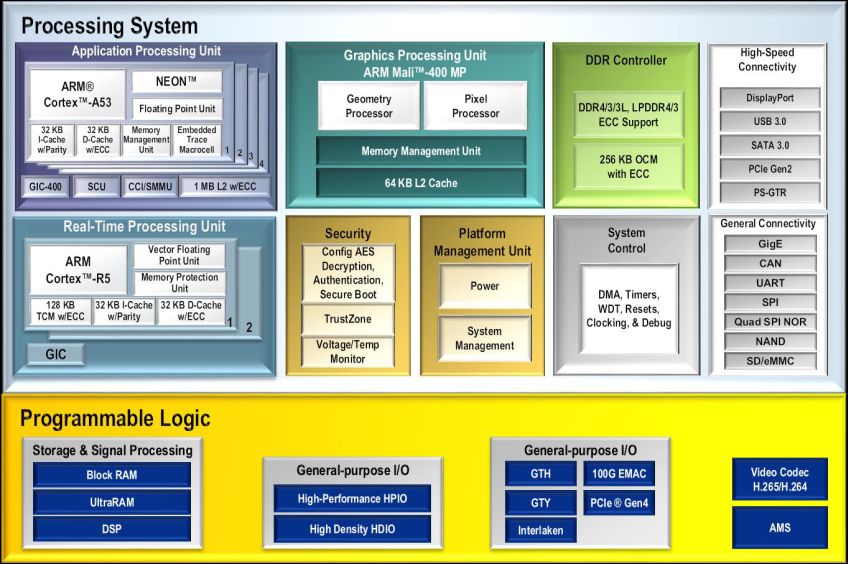

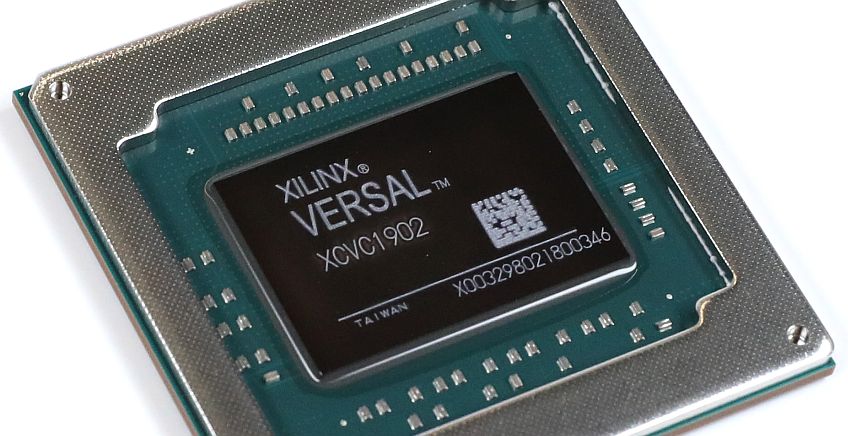

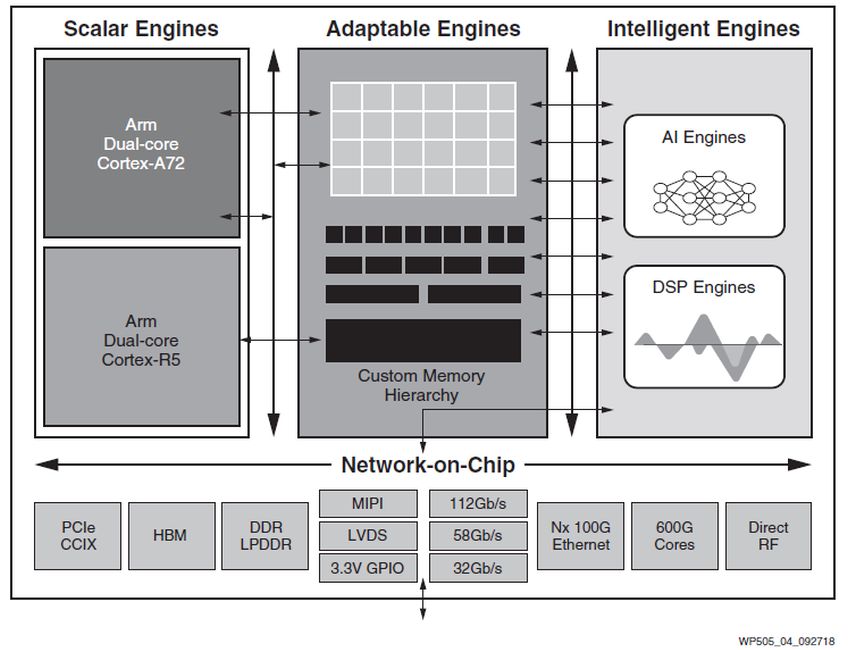

נשיאת ומנכ"לית AMD, ליסה סו (אשר נבחרה השבוע גם לתפקיד יו"ר החברה), אמרה ששילוב מוצרי זיילינקס – רכיבי FPGA, מעבדים מסתגלים (adaptive SoCs),מנועי בינה מלאכותית ותוכנה – יאפשרו ל-AMD להגדיל את משקלה בשוק יעד של תשתיות ענן, מחשוב קצה ואבזרים חכמים – שהיקפו נאמד בכ-135 מיליארד דולר ב-2023.

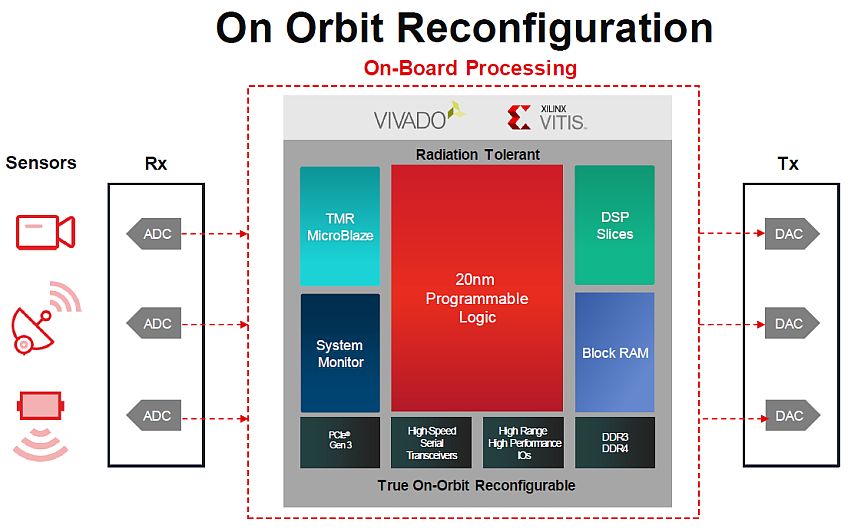

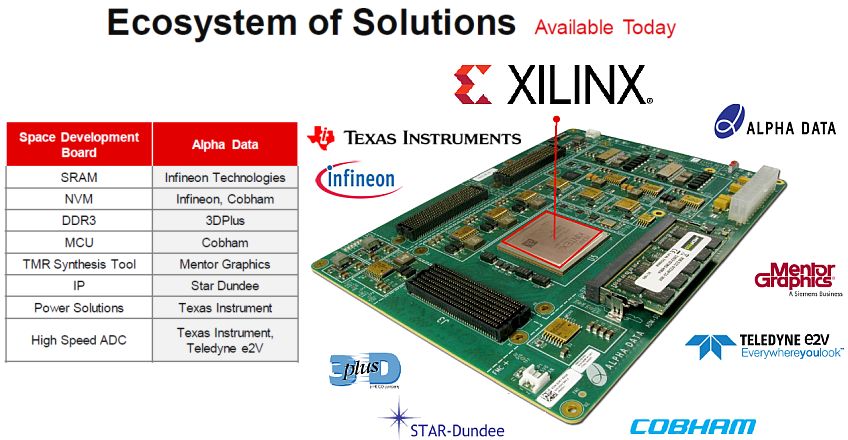

מהמצגת למשקיעים ש-AMD פירסמה בעקבות השלמת העיסקה מתברר שהיא מצפה להרוויח מהמיזוג בשלושה שווקים מרכזיים: בשוק מרכזי הנתונים המיזוג יאפשר לה לספק מתאמי תקשורת חכמים (SmartNIC), אשר ייסייעו לחזק את משפחת מעבדי השרתים AMD EPYC, הוא יסייע להביא את מעבדי AMD אל שוק המערכות המשובצות, שהוא השוק החזק ביותר של זיילינקס, ואולי הגורם החשוב ביותר שהביא למיזוג הוא פתיחת שוק התקשורת בפני AMD. לחברת זיילינקס יש קשרים הדוקים מאוד עם יצרניות ציוד תקשורת קווי ואלחוטי.

AMD צועדת בעקבות אינטל ואנבידיה

הקשרים האלה, ביחד עם המוצרים המשולבים, יכניסו את AMD לשוק שמבחינתה כמעט ולא היה קיים עד היום. במהלך הזה מיישרת AMD קו עם המתחרות הגדולות ביותר בתחום המחשוב: אינטל ואנבידיה, אשר מנהלות זמן רב אסטרטגיה של גישה רב-תחומית: שילוב מעבדי CPU, עם מעבדי עזר דוגמת GPU ועם פתרונות תקשורת חכמים למרכזי הנתונים. אלה היו השיקולים של אינטל כאשר היא רכשה בשנת 2015 את חברת ה-FPGA אלטרה (המתחרה הגדולה שלזיילינקס), ואלה היו השיקולים של אנבידיה כאשר היא רכשה בשנת 2-2- את חברת מלאנוקס הישראלית.

חברת AMD נמצאת בתנופה גדולה, ולפני שבועיים היא דיווחה שבשנת 2021 היא השיגה תוצאות שיא: מכירות הרבעון הרביעי צמחו ב-49% והסתכמו בכ-4.8 מיליארד דולר. החברה פרסמה תחזית צמיחה גם לשנת 2022. מכירות בהיקף של כ-5 מיליארד דולר ברבעון הראשון של השנה (צמיחה של 45% ביחס לרבעון המקביל), ומכירות שנתיות בהיקף של כ-21.5 מיליארד דולר – צמיחה של 31% בהשוואה לשנת 2021. ליסה סו רמזה שלהערכתה חלק גדול מהצמיחה יבוא על חשבון אינטל: "שוק ה-PC צפוי להיות שטוח ב-2022, אבל תחזית הצמיחה מבוססת על ההערכה שנוכל להגדיל את נתח השוק שלנו”.

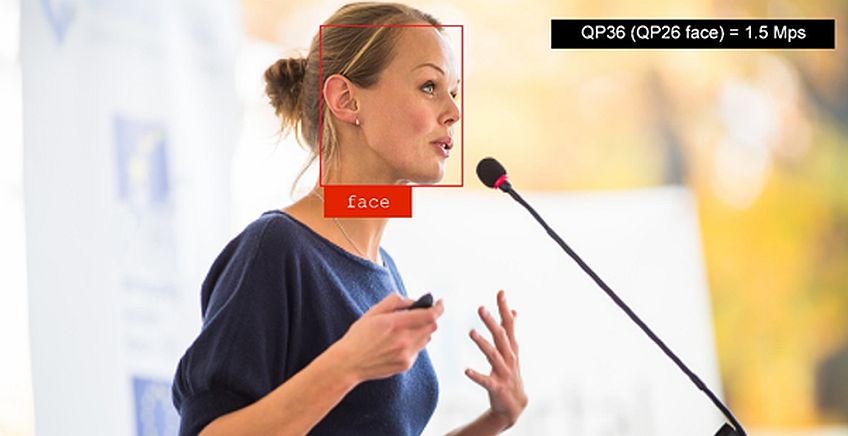

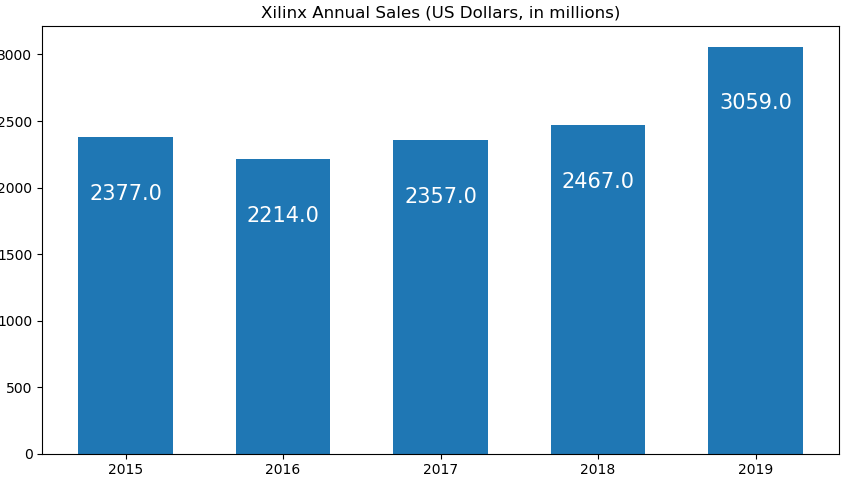

אחריו הגיע שוק התקשורת האלחוטית, שבו הדרישה לתשתיות 5G (בייחוד בקוריאה ובסין) הביאה לצמיחה של 34% במכירות. החברה מסרה שמכירותיה בתחום הרכב צמחו בשיעור "דו-ספרתי" אודות למעמדה בשוק מערכות ה-ADAS. בעקבות ההכרזה על ארכיטקטורת ACAP החדשה, עלתה מניית זיילינקס בנסד"ק מכ-104 דולר לכ-112 דולר למנייה, והחברה נסחרת כיום לפי שווי שוק של כ-28.47 מיליארד דולר.

אחריו הגיע שוק התקשורת האלחוטית, שבו הדרישה לתשתיות 5G (בייחוד בקוריאה ובסין) הביאה לצמיחה של 34% במכירות. החברה מסרה שמכירותיה בתחום הרכב צמחו בשיעור "דו-ספרתי" אודות למעמדה בשוק מערכות ה-ADAS. בעקבות ההכרזה על ארכיטקטורת ACAP החדשה, עלתה מניית זיילינקס בנסד"ק מכ-104 דולר לכ-112 דולר למנייה, והחברה נסחרת כיום לפי שווי שוק של כ-28.47 מיליארד דולר.